メモリセルの制御ゲートをワード線に引き出すステアケース:福田昭のストレージ通信(120) 3D NANDのスケーリング(8)(1/2 ページ)

今回は、「ステアケース(Staircase)のパターン形成」技術について解説する。特に注目したいのが、ステアケースのパターン形成を短時間で行える「トリム」技術だ。

セルトランジスタの制御ゲート層をワード線に接続

半導体メモリ技術に関する国際会議「IMW(International Memory Workshop)」では、カンファレンスの前日に「ショートコース(Short Course)」と呼ぶ1日間のセミナーを開催している。今年(2018年)5月に開催されたIMWのショートコースでは、9件の技術講座(チュートリアル)が午前から午後にかけて実施された。その中から、3D NANDフラッシュメモリ技術に関する講座「Materials, Processes, Equipment Perspectives of 3D NAND Technology and Its Scaling(3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望)」がとても参考になったので、その概要をシリーズでお届けしている。講演者は半導体製造装置の大手ベンダーApplied MaterialsのSean Kang氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回は、3D NANDフラッシュ製造における重要技術(キープロセス)の1つである「マルチペア(Multi-pair)薄膜の成膜(Deposition)」技術を解説した。今回は同じくキープロセスの1つである、「ステアケース(Staircase)のパターン形成」技術を説明していこう。

前回で解説したように、絶縁層と制御ゲート層のペア薄膜を積み上げることが、メモリセルを垂直に積み上げる構造のベースとなる。ここで問題となるのが、制御ゲート層をワード線として引き出し、最終的にはワード線デコーダーと接続しなければならないことだ。例えば32ペアのペア薄膜には32層の制御ゲート層が存在する。その各層から個別に、ワード線を引き出さなければならない。

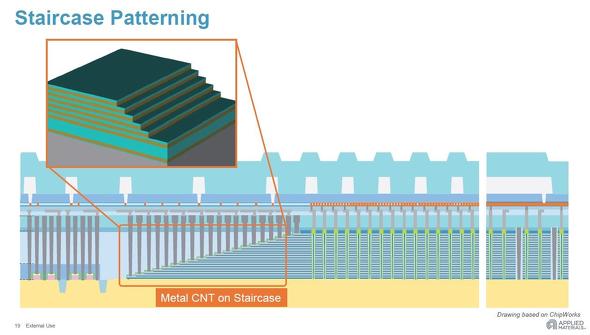

そのために必要となるのが、「ステアケース」と呼ばれる階段状の構造である。例えば32ペアのペア薄膜では、32段の階段状の構造を形成する。階段の各段の表面(建物や住宅などの階段で足が乗る部分に相当)が、制御ゲート層の表面である(厳密には制御ゲート層を保護するために、絶縁層が各段の表面にくる)。この表面から垂直に、細長いコンタクトを形成し、上方の金属配線層に形成したワード線と接続する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- 全固体電池の製造プロセス簡素化、東北大が新手法

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- NVIDIAとメモリ3社、世界半導体売上高の42%占める