絶縁膜の埋め込みと平坦化が、複雑な形状の加工を支える:福田昭のストレージ通信(124) 3D NANDのスケーリング(12)(1/2 ページ)

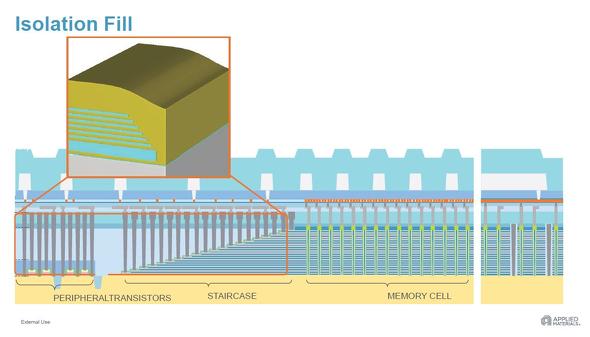

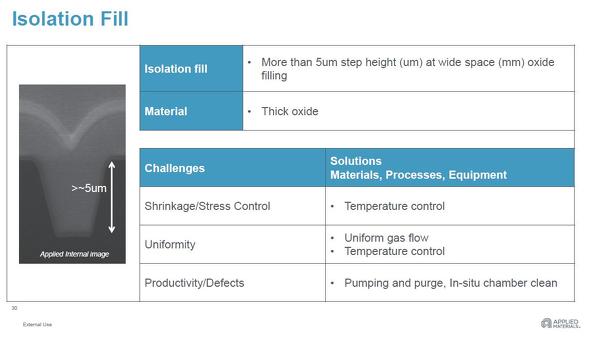

3D NANDフラッシュ製造における重要技術(キープロセス)の一つである「絶縁膜の埋め込み(Isolation Fill)」技術と、「平坦(へいたん)化(Planarization)」技術を紹介する。

深さ5μm前後、長さ数mmの複雑な形状に絶縁膜を埋め込む

半導体メモリ技術に関する国際会議「IMW(International Memory Workshop)」では、カンファレンスの前日に「ショートコース(Short Course)」と呼ぶ1日間のセミナーを開催している。今年(2018年)5月に開催されたIMWのショートコースでは、9件の技術講座(チュートリアル)が午前から午後にかけて実施された。その中から、3D NANDフラッシュメモリ技術に関する講座「Materials, Processes, Equipment Perspectives of 3D NAND Technology and Its Scaling(3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望)」がとても参考になったので、その概要をシリーズでお届けしている。講演者は半導体製造装置の大手ベンダーApplied MaterialsのSean Kang氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回は、3D NANDフラッシュ製造における重要技術(キープロセス)の一つである、「メモリセルの形成(Cell Formation)」技術を解説した。今回は、同じくキープロセスである「絶縁膜の埋め込み(Isolation Fill)」技術と、「平坦(へいたん)化(Planarization)」技術を紹介する。

本シリーズの第8回と第9回で説明したように、3D NANDフラッシュメモリでは「ステアケース」と呼ぶ階段状のパターンに並んだ制御ゲートと、周辺回路のゲート電極に対して、非常に細くて長いコンタクト電極を形成して最上層の金属配線とゲートを結線する必要がある。

ここでコンタクト用の細くて長い孔を形成する前にしておかなければならないのが、「絶縁膜による埋め込み」である。深さにして5μm前後と、長さにして数mmという深くて広くて複雑な形状(ステアケースとメモリセルのスリット)に、絶縁膜(シリコン酸化膜)を埋め込まなければならない。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Musk氏は「半導体製造の再定義」を目指すのか

- 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- 300mmファブ装置の投資額、2年連続で2桁成長へ

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- ヒューマノイドはどこまで現実になっているのか

- Intelがアイルランド工場を完全子会社化、Apolloから49%買い戻し