高密度化と大容量化の限界はまだ見えない:福田昭のストレージ通信(129) 3D NANDのスケーリング(15)(1/2 ページ)

「3D NANDのスケーリング」シリーズの最終回となる今回。前半では、3D NANDフラッシュのメモリセルアレイ以外の部分でシリコンダイ面積を削減する手法を解説し、後半では、3D NANDフラッシュの高密度化と大容量化を支える技術のロードマップを紹介する。

周辺回路とステアケースのシリコン面積を削減

半導体メモリ技術に関する国際会議「IMW(International Memory Workshop)」では、カンファレンスの前日に「ショートコース(Short Course)」と呼ぶ1日間のセミナーを開催している。今年(2018年)5月に開催されたIMWのショートコースでは、9件の技術講座(チュートリアル)が午前から午後にかけて実施された。その中から、3D NANDフラッシュメモリ技術に関する講座「Materials, Processes, Equipment Perspectives of 3D NAND Technology and Its Scaling(3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望)」がとても参考になったので、その概要をシリーズでお届けしている。講演者は半導体製造装置の大手ベンダーApplied MaterialsのSean Kang氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

本シリーズの前回では、メモリホールにおけるエッチングと成膜の難度を軽減する2つの手法を紹介した。今回は前半で、3D NANDフラッシュのメモリセルアレイ以外の部分でシリコンダイ面積を削減する、2つの手法を解説する。後半ではまとめとして、3D NANDフラッシュの高密度化と大容量化を支える技術のロードマップを紹介する。

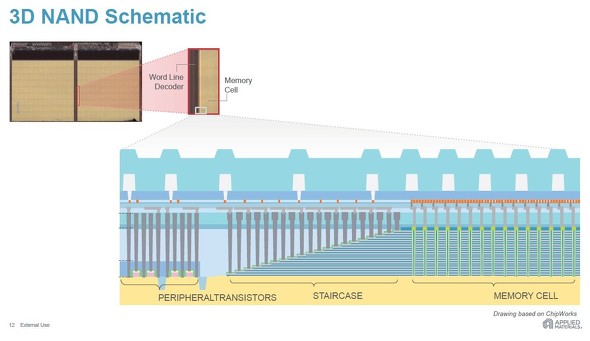

3D NANDフラッシュメモリの断面構造。左上はシリコンダイ写真。右下は、ワード線デコード回路とメモリセルアレイの境界付近を切り出した断面の構造図。構造図の左端は周辺回路。中央は制御ゲート(ワード線)の引き出し(ステアケース)。右端はメモリセルアレイ。出典:Applied Materials(クリックで拡大)

3D NANDフラッシュメモリの断面構造。左上はシリコンダイ写真。右下は、ワード線デコード回路とメモリセルアレイの境界付近を切り出した断面の構造図。構造図の左端は周辺回路。中央は制御ゲート(ワード線)の引き出し(ステアケース)。右端はメモリセルアレイ。出典:Applied Materials(クリックで拡大)3D NANDフラッシュメモリの断面構造を見るとすぐ分かるのが、メモリセルアレイ以外の部分によるシリコン面積がかなり存在することだ。1つは読み書きの制御やデータの外部入出力などを担う周辺回路のシリコン面積、もう1つはセルトランジスタの制御ゲートをワード線として引き出すための階段状部分(ステアケース)のシリコン面積である。これらの面積を削減すれば、シリコンダイの記憶密度をさらに向上できる。

始めは周辺回路について述べよう。3D NANDフラッシュのメモリセルアレイは、シリコン基板をまったく使っていない。原理的には、メモリセルアレイの直下にあるシリコン基板にトランジスタ回路を作り込める。周辺回路の一部あるいは大半をこのようにしてメモリセルアレイの直下に作り込むと、周辺回路が占めるシリコン面積を大幅に節約できる。

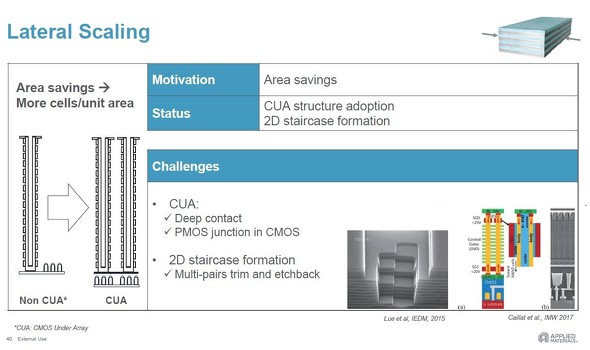

この「周辺回路とメモリセルアレイを積層する構造」を最初に開発して製品に適用したのは、3D NAND フラッシュ大手の一角を占めるIntelとMicron Technologyの共同開発連合である。両者はこの技術を「CUA(CMOS Under the Array)」と呼んだ。同様の技術はほかの3D NANDフラッシュ大手ベンダーも開発しており、一部は製品に導入済みだとみられる。ちなみに技術の名称は各社で違う。Samsung Electronicsは「COP(Cell Over Periphery)」、東芝メモリとWestern Digitalの連合は「CUA(Circuit-Under-Array)」、SK-Hynixは「PUC(Periphery Under Cell)」と呼んでいる。

次はステアケースである。高密度化のためにペア薄膜のペア数を増やすと、ステアケースのシリコン面積が増加する。このシリコン面積の増加は、ペア数が多くなればなるほど、無視できない問題となる。そこでステアケースの階段を現在のような直線状ではなく、螺旋(らせん)階段に近い2次元構造とすることで、ステアケースのシリコン面積を削減する技術が、国際学会で提案されている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長