高密度化と大容量化の限界はまだ見えない:福田昭のストレージ通信(129) 3D NANDのスケーリング(15)(2/2 ページ)

2021年にはペア薄膜の積層数は140ペアを突破

まとめとして、本シリーズの前々回と前回で述べた、3D NANDフラッシュの高密度化と大容量化の手法(スケーリング手法)を、過去から将来まで展望する。時間の範囲は2015年〜2021年である。

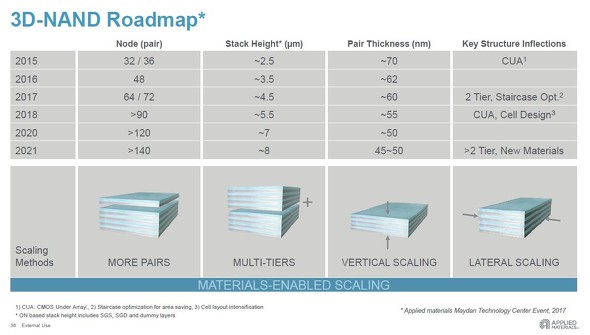

3D NANDフラッシュの高密度化と大容量化の手法(スケーリング手法)を2015年から2021年まで展望したもの。上はセルの積層数や寸法、要素技術などのロードマップ。下はスケーリング手法。出典:Applied Materials(クリックで拡大)

3D NANDフラッシュの高密度化と大容量化の手法(スケーリング手法)を2015年から2021年まで展望したもの。上はセルの積層数や寸法、要素技術などのロードマップ。下はスケーリング手法。出典:Applied Materials(クリックで拡大)基本的なスケーリング手法は「ペア薄膜のペア数を増やす(More Pairs)」ことだ。2015年には32/36ペアだったのが、2017年には2倍の64/72ペアとなった。2018年は90ペアを超えつつある。そして将来、2020年には120ペアを超え、さらに2021年には140ペアを超えるようになると予測する。

ペア数の増加によってメモリスタック全体の高さは徐々に増大していく。2015年にはおよそ2.5μmだったのが、2018年には2倍強のおよそ5.5μmとなった。メモリホールのアスペクト比が増加することによる製造の難しさを緩和するために、64/72ペアからは「マルチティア(Multi-Tiers)」を導入した。

さらに、ペア薄膜の厚みを少しずつ薄くする「バーティカル・スケーリング(Vertical Scaling)」が実施されてきた。ペア薄膜の厚みは2015年にはおよそ70nmだったのが、2018年にはおよそ55nmにまで縮まっている。ただし、これ以上はあまり薄くしにくい。50nm〜45nmが限界とみられる。

ちなみに2021年に達成すると予測された140ペアというペア数は、限界ではない。既にフラッシュメモリ業界では、500ペアという途方もない数が2018年の夏には議論され始めた。64ペア〜96ペアで、シリコンダイ当たりの記憶容量は1Tbitに達している。すると500ペアは、シリコンダイ当たりでは単純計算で5Tbit強になる。3D NANDフラッシュの高密度化と大容量化の限界は、まだ見えていない。

(「3D NANDのスケーリング」は今回で完結となります。ご愛読をありがとうございました)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

関連記事

3D NANDの高密度化を支えるペア薄膜のスケーリング手法

3D NANDの高密度化を支えるペア薄膜のスケーリング手法

「IMW(International Memory Workshop)」のショートコースから、3D NANDフラッシュメモリ技術に関する講座を紹介するシリーズ。今回からは、3D NANDフラッシュの高密度化と大容量化の手法(スケーリング手法)と、時間的なスケジュール(ロードマップ)をご紹介していく。 2xnm技術で試作した40Mビット埋め込みMRAM(前編)

2xnm技術で試作した40Mビット埋め込みMRAM(前編)

2xnm世代のCMOSロジック製造技術によって記憶容量が40Mビット(5Mバイト)の埋め込みMRAMマクロを試作した結果を、前後編で報告する。前編では、高温動作での読み出し電圧マージンの確保と、低温動作での書き込み電圧マージンの維持について紹介する。 埋め込みMRAMのメモリセルと製造プロセス

埋め込みMRAMのメモリセルと製造プロセス

今回は、ロジックへの埋め込みに向けたMRAMのメモリセルと製造プロセスについて解説する。 IoT/自動車向けMRAMに対する要求仕様とデータ書き換え特性

IoT/自動車向けMRAMに対する要求仕様とデータ書き換え特性

埋め込みフラッシュメモリの置き換えを想定したMRAM(eMRAM-F)と、埋め込みSRAMの置き換えを想定したMRAM(eMRAM-S)が、IoT(モノのインターネット)や自動車で使われる場合、どういった仕様が要求されるのか。データの書き換え特性を中心に解説する。 電力供給なしでトランジスタの電流を増幅

電力供給なしでトランジスタの電流を増幅

静岡大学電子工学研究所/創造科学技術大学院の小野行徳教授らは、NTTや北海道大学の研究グループと共同で、電力供給なしにトランジスタの電流を増幅させることに成功した。 SK Hynix、31億米ドルを投じメモリ新工場建設へ

SK Hynix、31億米ドルを投じメモリ新工場建設へ

SK Hynixは2018年7月27日、約31億米ドルを投じて、韓国にある本社に新たなDRAM製造施設を建設する計画を発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表