EE Times Japan >

プロセス技術 >

10nmで苦戦するIntel、問題はCo配線とRuバリアメタルか:湯之上隆のナノフォーカス(9)(2/5 ページ)

» 2019年02月18日 11時30分 公開

[湯之上隆(微細加工研究所),EE Times Japan]

Intelの10nmプロセスとは

Intelは2017年12月、サンフランシスコで開催された半導体の国際学会「IEDM」で、“A 10nm High Performance and Low-Power CMOS Technology Featuring 3rd Generation FinFET Transistors, Self-Aligned Quad Patterning, Contact over Active Gate and Cobalt Local Interconnects”のタイトルで発表し、世界で初めてコバルト(Co)配線を使ったことを明らかにした。

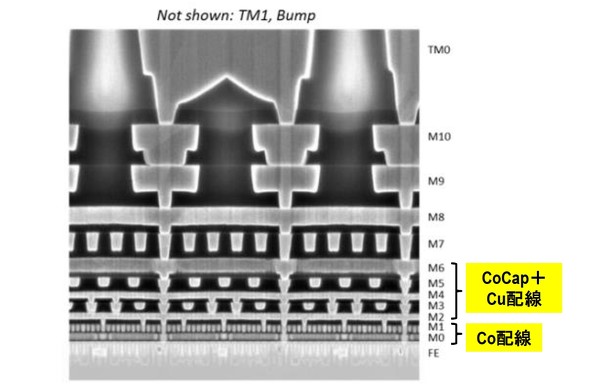

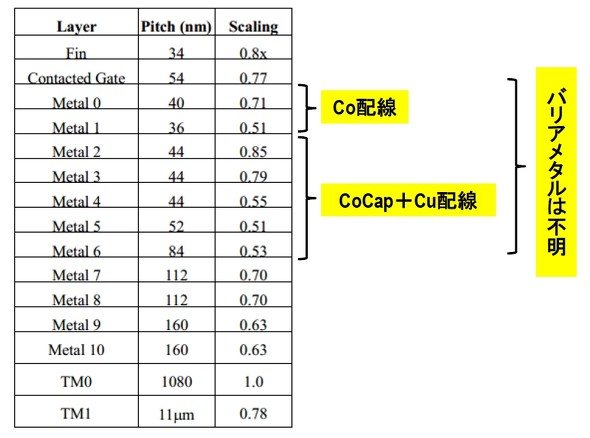

筆者は、2016年頃から、微細配線の材料がCuからCo、Ru(ルテニウム)、Mn(マンガン)などに変わるかもしれない兆候をつかんでいた。従って、この論文でIntelがCo配線を使ったことに注目した。Intelの上記論文によれば、M0とM1にCo配線を使用し、M2〜M6の配線にはCu配線とCoキャップを使ったと書かれている(図1、図2)。しかし、バリアメタル材料についての記載はない。

ここで、多層配線の構造が、バルク配線材料、バリアメタル、キャップから構成されていることを説明した上で、なぜ、CuからCoなどに配線材料が変更されなくてはならないのかを詳述する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR