東工大、極低消費電力のデジタルPLLを開発:SoCのエネルギー効率を改善

東京工業大学は、消費電力が極めて小さい分数分周タイプのデジタル位相同期回路(PLL)を開発した。従来の開発品に比べて消費電力を60%削減できるという。

サブサンプリングとサンプリングの動作を組み合わせ

東京工業大学工学院電気電子系の岡田健一准教授らによる研究グループは2019年2月、消費電力が極めて小さい分数分周タイプのデジタル位相同期回路(PLL)を開発したと発表した。従来の開発品に比べて消費電力を60%削減できるという。

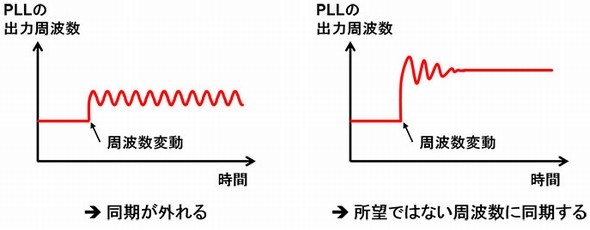

分数分周タイプのデジタルPLLは、電力消費が少なく回路面積も小さいことから、IoT(モノのインターネット)機器向けSoCなどの用途で注目されている。しかし、消費電力を500μW以下に抑える技術は、まだ報告されていないという。さらなる低消費電力を達成するために、サブサンプリング技術を応用することも検討されてきたが、これまではノイズの影響による誤動作などの課題があった。

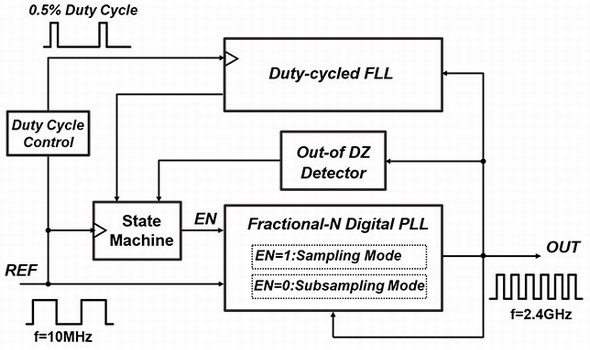

研究グループは今回、サブサンプリング動作とサンプリング動作を組み合わせることで、低消費電力化とPLLの誤動作回避の両立を実現した。具体的には、サンプリング動作時に、PLLの周波数がレファレンス周波数(REF)に同期すると、PLLの動作モードを消費電力の少ないサブサンプリング動作に切り替える。

PLLにはODZ(Out-of-deadzone)検出回路と周波数同期回路(FLL:frequency locked loop)が実装されている。ODZ検出回路はPLLの同期が外れた場合にそれを検出し、PLLの動作モードを自動的にサブサンプリング動作からサンプリング動作に切り替える。FLLは、PLLが望んでいない周波数に同期した場合に、その異常を検出してPLLの動作モードをサンプリングモードに切り替える。こうした方式を採用することで、サブサンプリング動作時の誤動作を防ぐことができるという。

ただ、FLLを通常動作させると消費電力の増大につながるという。そこで研究グループは、FLLを間欠動作させることにした。FLL内のカウンターについて動作デューティ比を0.5%まで低下させることによって、消費電力を大幅に削減した。通常動作のFLLを用いたサブサンプリングPLLに比べて、サブサンプリング動作時の消費電力は約70%も削減できることをシミュレーションで確認した。

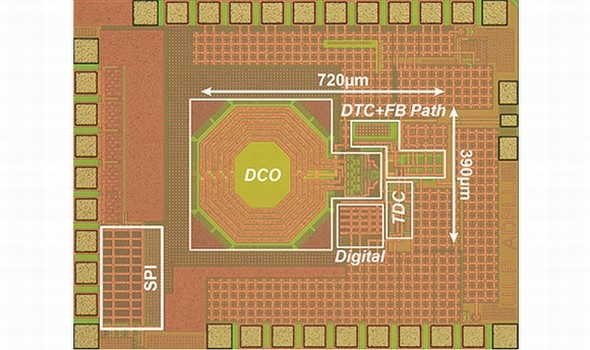

サブサンプリングとサンプリングを組み合わせる技術に加え、デジタル制御発振器(DCO)とデジタル時間変換器(DTC)の低消費電力化も実現した。これによって動作時におけるPLL全体の消費電力削減が可能となる。

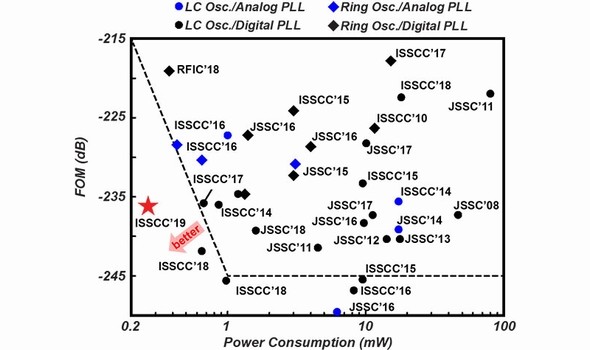

新たに開発した分数分周デジタルPLL回路は、最小配線半ピッチ65nmのシリコンCMOSプロセスで試作した。10MHzのレファレンス周波数から2.05〜3.10GHzを出力する。動作時の消費電力は265μWである。ジッタ特性を表すFoM(Figure of Merit)は−236.8dBとなった。これらのデータから、開発したPLLは出力信号の品質を維持したまま、消費電力の低減を実現できることを実証した。

研究グループによれば、開発した超低消費電力PLL技術をレシーバーに適用すると、消費電力は現行の約3mWに対して、ほぼ半分に削減できる見通しである。

なお、研究成果は半導体集積回路技術の国際学会「ISSCC(International Solid-State Circuits Conference) 2019」(2019年2月17〜21日、米国カリフォルニア州サンフランシスコ)で、その詳細を発表した。

関連記事

ISSCC 2019の目玉はAIと5Gに、CPUの話題は少ない?

ISSCC 2019の目玉はAIと5Gに、CPUの話題は少ない?

2019年2月17〜21日に米国カリフォルニア州サンフランシスコで開催される半導体回路技術関連の国際学会「ISSCC 2019」は、発表内容のほとんどが、機械学習(マシンラーニング)や高速ネットワーク、メモリが主役となる“データ時代”に関するものとなりそうだ。 広島大学ら、300GHz帯トランシーバーICを開発

広島大学ら、300GHz帯トランシーバーICを開発

広島大学、情報通信研究機構(NICT)、パナソニックは、シリコンCMOS回路を用いた300GHz帯ワンチップトランシーバーICを共同開発した。80Gビット/秒のデータ伝送が可能となる。 東工大ら、室温で電場による磁化反転を実証

東工大ら、室温で電場による磁化反転を実証

東京工業大学らの研究グループは、強磁性と強誘電性が共存するセラミック結晶について、室温で電場による磁石の極性を反転(磁化反転)させることに成功した。次世代磁気メモリの実現に弾みをつける。 東工大、振動発電素子のエレクトレットを外付け

東工大、振動発電素子のエレクトレットを外付け

東京工業大学(東工大)は、新原理の振動発電素子を東京大学と共同で開発し、発電することを確認した。開発した素子は、MEMS可変容量素子とエレクトレット層を個別に作製し、電気配線で接続する構造である。 トポロジカル絶縁体で高性能純スピン注入源開発

トポロジカル絶縁体で高性能純スピン注入源開発

東京工業大学は、トポロジカル絶縁体であるBiSb(ビスマスアンチモン)の(012)面方位を用いて、高性能の純スピン注入源を開発した。次世代スピン軌道トルク磁気抵抗メモリ(SOT-MRAM)を実現できる可能性が高まった。 指先に装着できる、CNTを用いた非破壊検査チップ

指先に装着できる、CNTを用いた非破壊検査チップ

東京工業大学らの研究グループは、材料にカーボンナノチューブ(CNT)膜を用いたテラヘルツ検査チップを開発した。検査チップを指先に取り付け、配管の亀裂検査などを非破壊で行うことが可能となる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

サブサンプリングPLLの誤動作の例 出典:東京工業大学

サブサンプリングPLLの誤動作の例 出典:東京工業大学 開発した分数分周タイプのデジタル位相同期回路のブロック図 出典:東京工業大学

開発した分数分周タイプのデジタル位相同期回路のブロック図 出典:東京工業大学 開発した開発したPLLのチップ写真 出典:東京工業大学

開発した開発したPLLのチップ写真 出典:東京工業大学 ISSCCで発表されたPLLのFoMと消費電力の関係 出典:東京工業大学

ISSCCで発表されたPLLのFoMと消費電力の関係 出典:東京工業大学