東芝、SSD向けにPAM4採用のブリッジチップ開発:高速かつ大容量の両立を可能に

東芝は、SSD(Solid State Drive)内に組み込まれるフラッシュメモリとコントローラICの間に挿入するブリッジチップを開発した。SSDにおいて高速化と大容量化の両立を可能にする技術である。

ブリッジチップとコントローラICをリング型デイジーチェーンで接続

東芝は2019年2月、SSD(Solid State Drive)内に組み込まれるフラッシュメモリとコントローラICの間に挿入するブリッジチップを開発したと発表した。少ない高速信号線で、より多くのフラッシュメモリを接続することができ、SSDにおいて高速化と大容量化の両立が可能となる。

SSDには、データの読み書きやエラー訂正などを行うコントローラICと、多くのフラッシュメモリが実装され、これらは高速のインタフェースで接続されている。SSDの動作速度を維持しようとすれば、1本のインタフェースに接続するフラッシュメモリ数が制限される。大容量を実現するには、多数のインタフェースが必要となり基板上への実装が難しくなる。

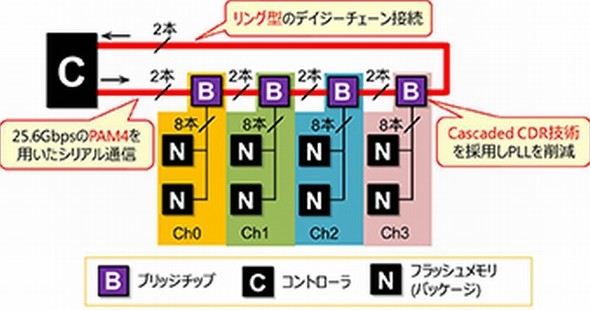

そこで東芝は、フラッシュメモリとコントローラICの間に挿入するブリッジチップを開発し、これらの課題を解決した。新たな接続方式は、ブリッジチップとコントローラICをリング型のデイジーチェーンで接続する。これにより、ブリッジチップ内に必要な送受信器は1対(従来は2対)で済み、チップ面積の削減を可能とした。

また、デイジーチェーンに接続したコントローラICとブリッジチップ間は、4値のデータ転送方式「PAM4(4-level Pulse Amplitude Modulation)」によるシリアル通信を採用した。これにより、ブリッジチップ内における回路の動作速度を低く抑えることができ、高い性能の送受信器を用いる必要がないという。さらに、新規開発のCDR(Clock Data Recovery)を用いてジッタ特性も改善した。これにより、ブリッジチップ上のPLL(Phase Locked Loop)が不要となった。

東芝は、開発したブリッジチップを28nmのCMOSプロセスで試作。4個のブリッジチップとコントローラICをリング型のデイジーチェーンで接続し、その特性を評価した。この結果、全てのブリッジチップとコントローラIC間で25.6Gビット/秒のPAM4通信が行われ、ビット誤り率(BER:Bit Error Rate)は10-12以下であることを確認した。

今回の研究成果は、半導体集積回路技術の国際会議「ISSCC(International Solid-State Circuits Conference) 2019」(2019年2月17〜21日、米国カリフォルニア州サンフランシスコ)で、現地時間2月20日に発表した。

関連記事

車載制御マイコン、ハードによる仮想化が可能に

車載制御マイコン、ハードによる仮想化が可能に

ルネサス エレクトロニクスは、次世代の車載制御マイコンに向けて、ハードウェアによる仮想化支援機構や、スタンバイ‐レジューム自己故障診断(SR‐BIST)機能などを開発した。フラッシュメモリ混載28nm低電力プロセスを用いてテストチップを試作し、これらの機能について動作を確認した。 東工大、極低消費電力のデジタルPLLを開発

東工大、極低消費電力のデジタルPLLを開発

東京工業大学は、消費電力が極めて小さい分数分周タイプのデジタル位相同期回路(PLL)を開発した。従来の開発品に比べて消費電力を60%削減できるという。 広島大学ら、300GHz帯トランシーバーICを開発

広島大学ら、300GHz帯トランシーバーICを開発

広島大学、情報通信研究機構(NICT)、パナソニックは、シリコンCMOS回路を用いた300GHz帯ワンチップトランシーバーICを共同開発した。80Gビット/秒のデータ伝送が可能となる。 ISSCC 2019の目玉はAIと5Gに、CPUの話題は少ない?

ISSCC 2019の目玉はAIと5Gに、CPUの話題は少ない?

2019年2月17〜21日に米国カリフォルニア州サンフランシスコで開催される半導体回路技術関連の国際学会「ISSCC 2019」は、発表内容のほとんどが、機械学習(マシンラーニング)や高速ネットワーク、メモリが主役となる“データ時代”に関するものとなりそうだ。 AIプロセッサを開発した東芝メモリの狙い

AIプロセッサを開発した東芝メモリの狙い

東芝メモリは2018年11月6日、ディープラーニング専用のプロセッサを開発したと発表した。今回同社が開発したのは、推論向けの技術。アルゴリズムとハードウェアの協調設計により、従来の方法に比べて認識精度をほとんど劣化させずに演算量を削減し、推論の高速化と低消費電力化を図ることに成功した。 IoT機器の固体認証向け新PUF技術、東芝が開発

IoT機器の固体認証向け新PUF技術、東芝が開発

東芝は、IoT(モノのインターネット)機器の固体認証を行うための物理複製困難関数(PUF:Physically Unclonable Function)技術を開発。自走ロボットに搭載し、機器間の相互認証が可能であることを確認した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

ブリッジチップを用いた接続と新たに開発した技術 出典:東芝

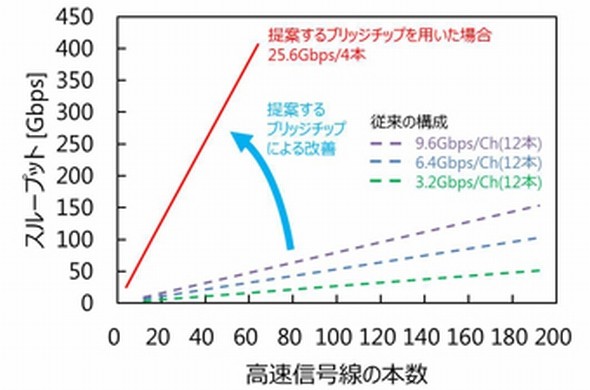

ブリッジチップを用いた接続と新たに開発した技術 出典:東芝 ブリッジチップを用いた場合と従来構成で得られた特性の比較 出典:東芝

ブリッジチップを用いた場合と従来構成で得られた特性の比較 出典:東芝