DRAMのスケーリング論:福田昭のストレージ通信(140) 半導体メモリの技術動向を総ざらい(3)(1/2 ページ)

今回はDRAMのスケーリングと、次世代メモリへのニーズが高まっている背景を取り上げる。

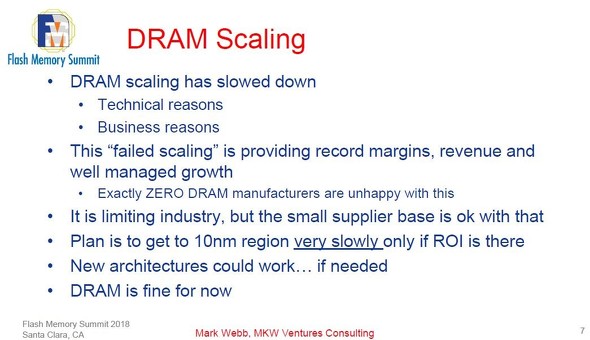

スローダウンするDRAMの微細化ペース

2018年8月に米国シリコンバレーで開催された、フラッシュメモリとその応用製品に関する世界最大のイベント「フラッシュメモリサミット(FMS:Flash Memory Summit)」で、市場調査会社MKW Venture Consulting, LLCでアナリストをつとめるMark Webb氏が、「Annual Update on Emerging Memories」のタイトルで講演した半導体メモリ技術に関する分析を、シリーズでご紹介している。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

本シリーズの前回では、次世代メモリ(New Memories)に期待する理由を挙げるとともに、現行世代メモリの代表であるNANDフラッシュメモリのスケーリング(微細化と高密度化)を論じた。今回は同じく現行世代メモリの代表である、DRAMのスケーリング(微細化と高密度化)における現状をご説明する。

DRAMの記憶密度の向上は基本的には、製造技術の微細化、すなわち加工寸法を細くすることによって進んできた。例えば2000年代まで、微細化の世代交代は、加工寸法を前の世代の約0.7倍に短くすることで、達成されていた。ただし最近ではリソグラフィ技術の微細化が停滞しつつあることから、DRAM製造の微細化ペースは非常にゆっくりとしたものになっている。

DRAM製品の最新世代は20nm世代を切った1Xnm世代あるいは1Ynm世代である。半導体ロジックの製造技術世代は、22nmから16/14nm、10nm、そして7nmと微細化が進んできた。20nmから10nmまでの世代は、2世代しかない。ところがDRAMでは2世代では終わらず、20nmから10nmまでの世代の数がロジックよりもはるかに多い。

具体的には、最初の世代である1Xnm世代の次に、微細化を進めた1Ynm世代が来る。その次は、1Znm世代、さらにその次は1アルファ(α)nm世代、その先には1ベータ(β)nm世代というロードマップが描かれている。20nm未満で10nmまでの間に、少なくとも5つの世代が入る。仮に1X世代が18nm、1β世代が10nmだとすると、その間の世代は平均すると2nmと、微細化による加工寸法の縮小はごくわずかなものにしかならない。加工寸法の大幅な縮小はもはや不可能だと言える。

微細化の困難さを緩和して記憶密度を高める手段は、3次元化である。DRAMのメモリセルは、1個のセル選択用MOSトランジスタと1個のキャパシターで構成される。メモリセルはワード線およびビット線と接続する。ここでキャパシターを細く高くすることで、シリコン面積を節約する。さらにはセル選択用MOSトランジスタのワード線とチャンネルをシリコン基板に埋め込む、メモリセルアレイのレイアウトを高密度化する、といった工夫がなされている。

もう1つ重要なのが、DRAMビジネスの特殊性である。DRAMのチップ価格は非常に低い水準に抑え込まれている。このため、DRAM大手メーカーは、非常に大きな数量のチップを量産することにより、チップ当たりの製造コストを下げている。製造設備への投資金額は莫大であり、リスクは小さくない。過去に何度も発生したチップ価格の暴落により、DRAMメーカーの数は徐々に減ってきた。現在では、DRAMの大手メーカーはわずか3社しかない。

大手メーカーが3社しかないということは、競争原理が働きにくい、ということでもある。微細化を大幅に進めてリスクを取る意味は、あまりない。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増