組み込みAIを加速する、ルネサスの新Processing-in-Memory:低電力で高速な推論を実現する(3/4 ページ)

» 2019年06月13日 11時30分 公開

[村尾麻悠子,EE Times Japan]

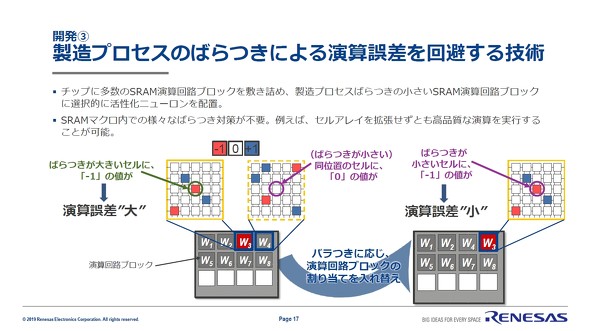

演算回路ブロックを入れ替えて製造ばらつきを低減

3つ目が、製造プロセスのばらつきによる演算誤差を回避する技術の開発だ。製造プロセスがばらつくと、ビット線電流の値に誤差が生じ、それがメモリデータ読み出しの誤差につながってしまう。例えば、ばらつきが大きいメモリセル(異常に大きな電流を流してしまうメモリセル)に「−1」や「+1」といった重みデータが格納されてしまうと、積和演算の結果が大きく違ってしまう可能性がある。一方で、もしそのセルに格納されている重みデータが「0」ならば、掛け算の結果は常にゼロになるので電流は流れず、積和演算の結果に影響がない。

新しいPIMでは、この原理を利用したという。チップに多数のSRAM演算回路ブロックを敷き詰め、ばらつきの大きいセルに「−1」や「+1」の重みデータが格納されたブロックがあった場合、すぐ隣のブロックと重み情報を入れ替えるという仕組みだ。

前述したように、活性化しているニューロンは基本的に極めて少ない。そのため、ほとんどの3値セルには「0」が格納されている。つまり、隣のブロックの同じ番地には『0』が入っている確率が非常に高い。ブロックを入れ替えれば、ばらつきが大きいセルに『0』が入る可能性が高く、掛け算の結果をゼロにできるのだ。

ただし、野瀬氏によると、メモリセルのばらつきを検出する方法は「検討中」だという。

図の「W1」「W2」などが演算回路ブロック。この中に、3値メモリセルが入っている。ばらつきに応じて、演算回路ブロックを隣のブロックと、そっくりそのまま入れ替えることで、演算誤差を回避できるとする 出典:ルネサス(クリックで拡大)

図の「W1」「W2」などが演算回路ブロック。この中に、3値メモリセルが入っている。ばらつきに応じて、演算回路ブロックを隣のブロックと、そっくりそのまま入れ替えることで、演算誤差を回避できるとする 出典:ルネサス(クリックで拡大)「演算回路ブロックを入れ替えるだけでいいので、冗長セルなどを入れずに演算誤差を大幅に低減できる」(野瀬氏)

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR