組み込みAIを加速する、ルネサスの新Processing-in-Memory:低電力で高速な推論を実現する(4/4 ページ)

» 2019年06月13日 11時30分 公開

[村尾麻悠子,EE Times Japan]

試作チップでも推論精度が落ちず

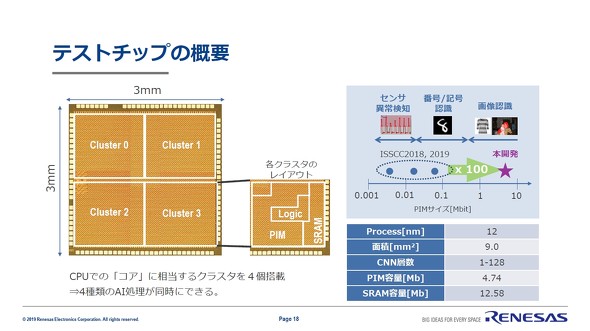

ルネサスは、開発した新しいPIMをベースにAIアクセラレーターを開発し、それを実装したテストチップを作成した。PIMの他、制御するためのロジックブロック、入出力情報を保持するためのSRAMブロックで構成されるクラスタが、4基搭載されている。クラスタは、CPUのコアに相当するもので、今回のように4基搭載している場合、4種類のAI処理を同時に行えるという。

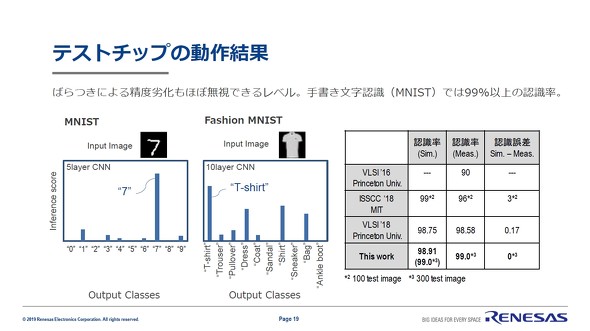

テストチップで、幾つかのCNNを動作させた結果。図の右側にある表に示している通り、これまでの論文では、手書き文字の認識率について、テストチップでの認識率(Meas.)はシミュレーションでの認識率(Sim.)に比べて数パーセント下がる場合が多かった。ルネサスのテストチップは、シミュレーションでの認識率(98.91)と実機での認識率(99.0)がほぼ一致している 出典:ルネサス(クリックで拡大)

テストチップで、幾つかのCNNを動作させた結果。図の右側にある表に示している通り、これまでの論文では、手書き文字の認識率について、テストチップでの認識率(Meas.)はシミュレーションでの認識率(Sim.)に比べて数パーセント下がる場合が多かった。ルネサスのテストチップは、シミュレーションでの認識率(98.91)と実機での認識率(99.0)がほぼ一致している 出典:ルネサス(クリックで拡大)野瀬氏は「従来のPIM関連の技術発表は、原理実証するだけのものが多く、画像認識のニューラルネットワークをチップ内で完結できる機能を搭載しているようなものはなかった。われわれが今回試作したチップは、チップ内部でシステムレベルの動作が可能になっている」と述べた。

左=ルネサスが行った、手書き文字認識のデモ。左の手前にあるのがテストチップを搭載した基板で、コイン電池で駆動する。手書き文字をカメラで撮影し、テストチップで推論させる/中央=ディスプレイの赤枠内の手書き文字を認識し、推論している。推論結果はディスプレイの左上に表示されている。左端に見えているオレンジの横棒は0〜9に相当する10本があり、棒の長さが長いほど、推論結果の“自信度”が高い。この写真では「0」と「6」に相当する横棒が長く伸びており、ニューラルネットワークが「0」か「6」だと推論していることが分かる/右=基板の右寄りにある一番大きなチップが試作チップ(クリックで拡大)

左=ルネサスが行った、手書き文字認識のデモ。左の手前にあるのがテストチップを搭載した基板で、コイン電池で駆動する。手書き文字をカメラで撮影し、テストチップで推論させる/中央=ディスプレイの赤枠内の手書き文字を認識し、推論している。推論結果はディスプレイの左上に表示されている。左端に見えているオレンジの横棒は0〜9に相当する10本があり、棒の長さが長いほど、推論結果の“自信度”が高い。この写真では「0」と「6」に相当する横棒が長く伸びており、ニューラルネットワークが「0」か「6」だと推論していることが分かる/右=基板の右寄りにある一番大きなチップが試作チップ(クリックで拡大)「e-AI」の処理性能を10倍にする要素技術

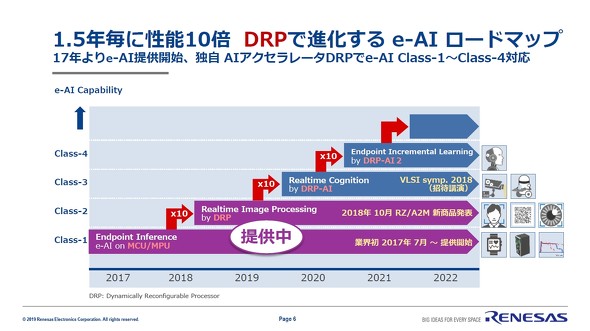

ルネサスは、e-AIの処理性能を1年半ごとに10倍にするというロードマップを持っているが、今回の新しいPIMは、10TOPS/Wクラスの性能を実現するための要素技術の一つになると位置付けている。

関連記事

「e-AI」で破壊的なイノベーションを、ルネサス 横田氏

「e-AI」で破壊的なイノベーションを、ルネサス 横田氏

ドイツ・ミュンヘンで開催中の「electronica 2018」に出展しているルネサス エレクトロニクスの展示内容は、車載製品ではなく、産業機器向けの製品が中心となっている。同社執行役員常務兼インダストリアルソリューション事業本部長を務める横田善和氏に、その狙いなどを聞いた。 組み込みAIをけん引する、ルネサスの意気込み

組み込みAIをけん引する、ルネサスの意気込み

ルネサス エレクトロニクスは「electronica 2018」(2018年11月13〜16日、ドイツ・ミュンヘン)で、同社が提唱する、組み込み機器にAI(人工知能)を搭載する「e-AI」の訴求に力を入れた。 環境発電で動作するコントローラー、ルネサスがSOTBを初適用

環境発電で動作するコントローラー、ルネサスがSOTBを初適用

ルネサス エレクトロニクス(以下、ルネサス)は2018年11月14日(ドイツ時間)、ドイツ・ミュンヘンで開催中の「electronica 2018」(2018年11月13〜16日)で、IoT(モノのインターネット)機器向けにエナジーハーベスト(環境発電)で得たエネルギーで駆動できる組み込みコントローラー「R7F0E」を発表した。2019年7月にサンプル出荷を開始し、同年10月より量産を開始する。 環境発電で“欠けていたピース”埋める、ルネサスのSOTB

環境発電で“欠けていたピース”埋める、ルネサスのSOTB

ルネサス エレクトロニクスはドイツ・ミュンヘンで開催された「electronica 2018」(2018年11月13〜16日)で、エナジーハーベスト(環境発電)で得たエネルギーで駆動できる組み込みコントローラー「R7F0E」を発表した。核となるのはルネサス独自のプロセス技術「SOTB(Silicon On Thin Buried Oxide)」である。 ルネサス、古い装置でもAIが使えるソリューション

ルネサス、古い装置でもAIが使えるソリューション

ルネサス エレクトロニクスは2017年11月27日、製造装置に、異常検知機能や予防保全機能など、AI(人工知能)を活用したインテリジェント機能を容易に付加できる「AIユニットソリューション」を開発し、販売を開始したと発表した。 家電でモーターの故障検知を実現する組み込みAI技術

家電でモーターの故障検知を実現する組み込みAI技術

ルネサス エレクトロニクス(以下、ルネサス)は2019年1月21日、白物家電などでモーターの故障検知が行えるマイコンベースのソリューションを発表した。低価格のマイコン上で学習済みのモーター故障検知AIを実行し、モーターの異常を検知し、アラートの発報などが行える。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR