1個のパッケージでシステムを実現するSiP:福田昭のデバイス通信(214) 2019年度版実装技術ロードマップ(25)(1/2 ページ)

今回は、SiP(System in Package)を実現する幾つかの手法のうち、2.X次元(2.XD)の実装技術を解説する。ここでカギとなるのは、インタポーザだ。

1個のパッケージで小さく薄いシステムを構成

電子情報技術産業協会(JEITA)が発行した「2019年度版 実装技術ロードマップ」に関する完成報告会(2019年6月4日に東京で開催)と同ロードマップの概要をシリーズでご報告している。今回はその第25回である。

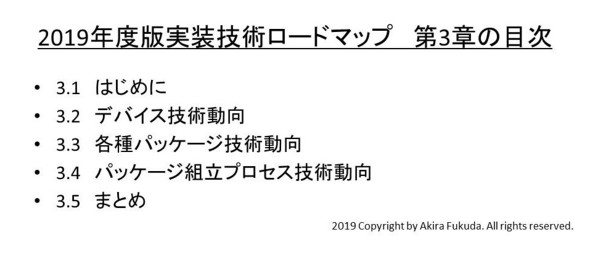

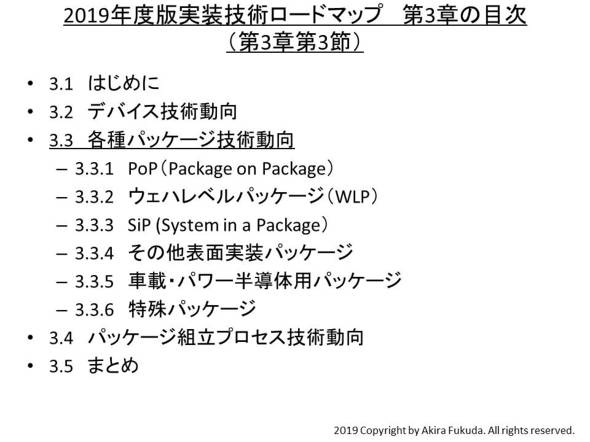

前々回から、第3章「電子デバイスパッケージ」の概要を紹介している。「電子デバイスパッケージ」は第1節から第5節までの5つの節によって構成される。「3.1 はじめに」から「3.2 デバイス技術動向」「3.3 各種パッケージ技術動向」「3.4 パッケージ組立プロセス技術動向」「3.5 まとめ」である。前回から「3.3 各種パッケージ技術動向」の内容をご紹介している。

2019年6月4日に東京で開催された「2019年度版 実装技術ロードマップ」完成報告会のプログラム。前々回から第3章「電子デバイスパッケージ」(プログラムの7番)の概要を解説している。出典:JEITA(クリックで拡大)

2019年6月4日に東京で開催された「2019年度版 実装技術ロードマップ」完成報告会のプログラム。前々回から第3章「電子デバイスパッケージ」(プログラムの7番)の概要を解説している。出典:JEITA(クリックで拡大)前回の末尾で説明したように、複数のシリコンダイを1個のパッケージにまとめることによって小さく薄いシステムを実現する、「SiP(System in Package)」が注目を集めている。SiPは機能別、あるいは製造技術別に異なるシリコンダイを組み合わせるので、SoC(Sysytem on a Chip)に比べると開発期間が大幅に短く、用途別のシステムを組みやすい。製造コストでも有利になることが多い。

SiPの実現手法には、PoP(Package on Package)やFO-WLP(Fan Out-Wafer Level Package)、FBGA(Fine-pitch Ball Grid Array)、3次元(3D)実装、2.X次元(2.XD)実装などの技術が存在する。中でも盛んに研究されているのが、3次元(3D)実装と2.X次元(2.XD)実装のSiPである。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増