部品内蔵基板の組み立て技術:福田昭のデバイス通信(219) 2019年度版実装技術ロードマップ(30)(2/3 ページ)

半導体チップや受動部品などをプリント基板の内部に収容

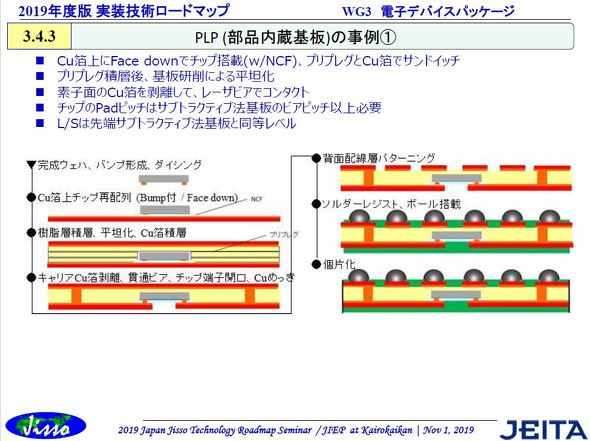

プリント配線基板に半導体チップや受動部品などを内蔵させる手法はいくつかある。ここでは3通りの組み立て技術をご紹介しよう。始めは半導体チップ(シリコンダイ)をフェースダウン(回路面を下にした状態)で基板に搭載する技術である。

完成ウエハーの回路面に銅(Cu)バンプを形成し、シリコンダイを切り出す。このシリコンダイをフェースダウンで銅箔(Cu箔:薄いCu箔と厚い支持用Cu箔で構成)に非導電フィルム(NCF:Non Conductive Film)を介して接続する。次にシリコンダイに相当する部分に穴を開けてあるプリプレグをプレス積層して、最上層を平坦化した後でCu箔を積層する。続いて支持用のCu箔を剥離し、上下のCu層間を貫通するビアを形成し、シリコンダイの回路側にレーザーで穴を開ける。次にCuめっきとエッチングを繰り返すことで再配線層を形成する。

それからシリコンダイの背面(裏面)側でCu層をパターニングする。ソルダーレジストを基板の両面に塗布してパターニングし、基板の背面にはんだボールを搭載する。最後に個別のパッケージあるいはモジュールとして基板を分割する。再配線層の線幅/間隔は25μm〜35μm/25μm〜35μmとやや広い。

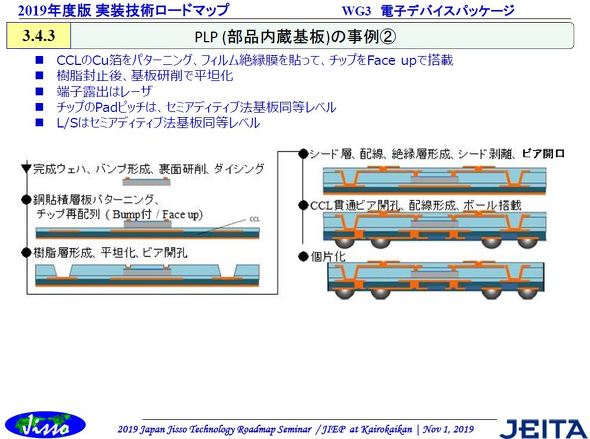

ここからは、シリコンダイをフェースアップ(回路面を上にした状態)で基板に搭載する技術をご説明しよう。完成ウエハーの回路面にCuバンプを形成し、ウエハーの裏面を研削し、シリコンダイを切り出す。

次に銅貼積層板(CCL:Copper Clad Laminate)のシリコンダイ搭載側Cu層をパターニングする。続いてパターニングした基板表面に絶縁フィルムを貼る。そして銅貼積層板(CCL)にシリコンダイをフェースアップで搭載し、全体を樹脂層で覆う。樹脂層の表面を平坦化し、シリコンダイのCuバンプ部分とCCL表面のCu箔部分が露出するようにレーザーで孔を開ける。

それから樹脂層表面にCuメッキとエッチング、樹脂層形成を繰り返して再配線層を形成する。再配線の形成が完了したら、底部のCCLを貫通するビアを作り、底面(裏面)に配線パターンを形成する。続いてはんだボールを底面に搭載する。最後に個別のパッケージあるいはモジュールとして基板を分割する。再配線層の線幅/間隔は25μm〜35μm/25μm〜35μmとやや広い。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増