EE Times Japan >

部品/材料 >

超スマート社会(Society 5.0)の実現を支援する電子部品:福田昭のデバイス通信(221) 2019年度版実装技術ロードマップ(31)(2/2 ページ)

» 2020年01月07日 13時30分 公開

[福田昭,EE Times Japan]

2019年版におけるインダクタ、コンデンサ、抵抗器の更新内容

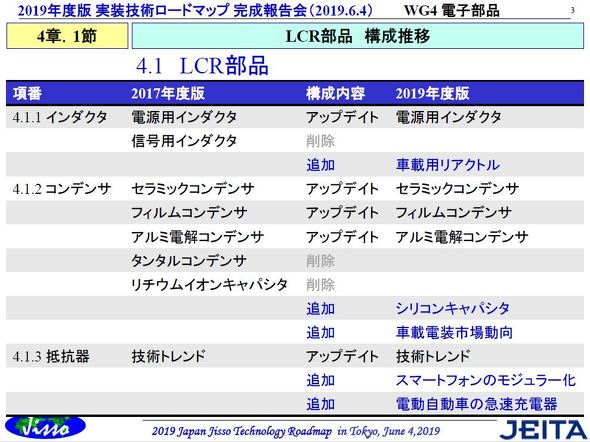

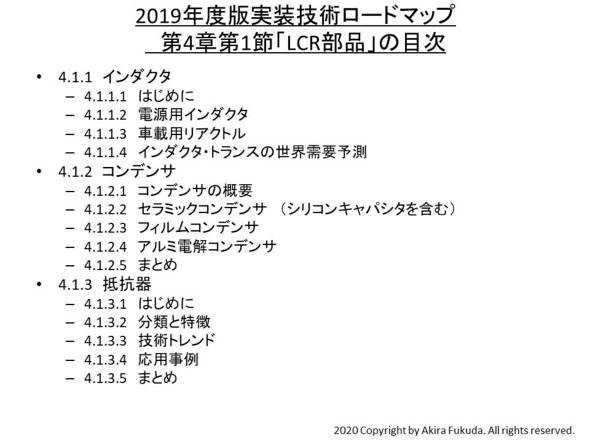

ここからは第4章第1節の「4.1 LCR部品」の概要を2017年度版(前回発行版)の実装技術ロードマップと比較しながら、説明していこう。「4.1 LCR部品」は、第1項の「4.1.1 インダクタ」と、第2項の「4.1.2 コンデンサ」、第3項の「4.1.3 抵抗器」で構成されている。

「4.1.1 インダクタ」は、2017年度版では電源用インダクタと信号用インダクタを取り上げていた。2019年度版では電源用インダクタの内容を更新するとともに、信号用インダクタを削除した。そして車載用リアクトルの説明を新たに追加した。

「4.1.2 コンデンサ」は、2017年度版ではセラミックコンデンサとフィルムコンデンサ、アルミ電解コンデンサ、タンタルコンデンサ、リチウムイオンキャパシタを解説していた。2019年度版ではセラミックコンデンサとフィルムコンデンサ、アルミ電解コンデンサの内容を更新するとともに、タンタルコンデンサとリチウムイオンキャパシタを削除した。そしてシリコンキャパシタを追加するとともに、車載用電装品市場でのコンデンサの動向を記述した。

「4.1.3 抵抗器」は、2017年度版では技術動向を説明していた。2019年度版では技術動向の内容をアップデートするとともに、応用事例としてスマートフォンのモジュラー化と、電動自動車の急速充電器を取り上げて解説を加えた。

各部品の概要については次回以降に順次、説明を加えていきたい。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

1個のパッケージでシステムを実現するSiP

1個のパッケージでシステムを実現するSiP

今回は、SiP(System in Package)を実現する幾つかの手法のうち、2.X次元(2.XD)の実装技術を解説する。ここでカギとなるのは、インタポーザだ。 多ピンと小型・薄型・低コストを両立させるFO-WLPの組み立て技術

多ピンと小型・薄型・低コストを両立させるFO-WLPの組み立て技術

パッケージの組み立てプロセス技術を紹介している。今回は、FO-WLP(Fan Out-Wafer Level Package)の組み立て工程を解説する。 日本の半導体産業は今後どうすべきなのか

日本の半導体産業は今後どうすべきなのか

筆者は仲間とともに半導体設計開発会社を興すに至った。今回は私事で大変、恐縮ではあるが、新会社に対するこだわりについて述べたいと思う。 新イーサネット規格「SPE」対応のコネクター

新イーサネット規格「SPE」対応のコネクター

HARTING Technology Groupは、新しいイーサネット規格であるシングルペアイーサネット(以下、SPE)に準拠したコネクター「HARTING T1 Industrial」を発表した。 接続箇所が“色”で分かる、カラフルなコネクター

接続箇所が“色”で分かる、カラフルなコネクター

日本端子は「CEATEC 2019」(2019年10月15〜18日、幕張メッセ)で、複数のヘッダを集約する際、接続する箇所を色で分かるようにした小型のマルチコネクター「Color Block Connector」などを展示した。 「世界最小」SAWデバイスを製品化、村田製作所

「世界最小」SAWデバイスを製品化、村田製作所

村田製作所は2019年7月16日、従来製品に比べサイズを24〜37%小型化したSAW(Surface Acoustic Wave/表面弾性波)デバイスを製品化し、量産を開始したと発表した。同社では、SAWデバイスとして「世界最小サイズを実現すると同時に、従来品と同等以上の特性を持つ」としている。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR