1nmが見えてきたスケーリング 「VLSI 2020」リポート:湯之上隆のナノフォーカス(27)(3/7 ページ)

配線抵抗増大の問題

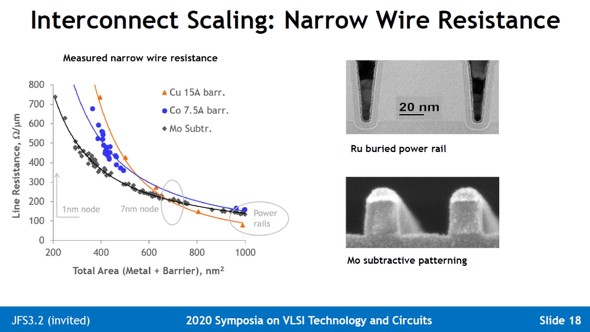

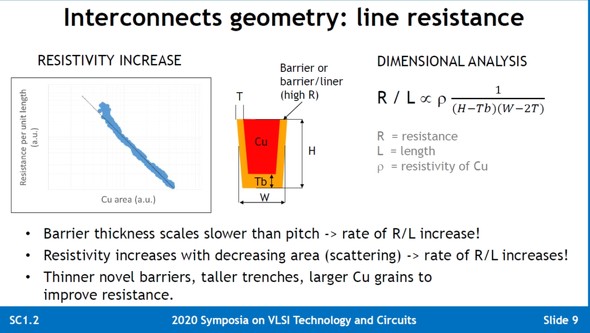

スケーリングの進歩とともに、新たなトランジスタ構造が考案されている。その一方、多層配線は、極めて深刻な問題に直面している。現在、多層配線の材料にはCuが用いられているが、Cuは絶縁膜中を拡散してしまうために、TaやTaNなどのバリアメタルが必要となっている。ところが、配線幅を微細化しても、ある一定以上の膜厚のバリアメタルが必要であるため、バリアメタルを含めたCu配線の抵抗が微細化とともに急増してしまうのである(図9)。

図9:配線断面積の縮小と配線抵抗の増加 出典:Mauro Kobrinsky, Intel, “On-Die Interconnect Challenges and Opportunities for Future Technology Nodes”, VLSI 2020, SC1.2(クリックで拡大)

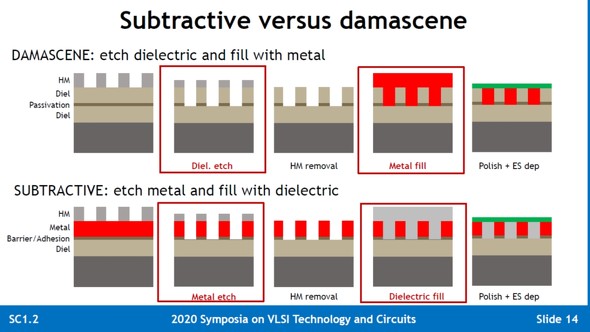

図9:配線断面積の縮小と配線抵抗の増加 出典:Mauro Kobrinsky, Intel, “On-Die Interconnect Challenges and Opportunities for Future Technology Nodes”, VLSI 2020, SC1.2(クリックで拡大)この問題を解決するために、IntelのMauro Kobrinsky氏は、最も微細な配線(M1)について、従来のダマシン(Damascene)法ではなく、メタルを直接ドライエッチングするSubtractive法を提案している(図10)。

図10:メタル配線の形成方法 ダマシンと直接加工 出典:Mauro Kobrinsky, Intel, “On-Die Interconnect Challenges and Opportunities for Future Technology Nodes”, VLSI 2020, SC1.2(クリックで拡大)

図10:メタル配線の形成方法 ダマシンと直接加工 出典:Mauro Kobrinsky, Intel, “On-Die Interconnect Challenges and Opportunities for Future Technology Nodes”, VLSI 2020, SC1.2(クリックで拡大)実は、メタルの直接加工は、Cuを使う前のAl配線で用いられていた方法だった。ところが、CuはAlよりも配線抵抗が低いが、その直接加工が極めて難しかった。そこで、絶縁膜に溝や孔を加工してバリアメタルを介してCuで埋め込み、不要な部分をCMPで除去する、いわゆるダマシン法が使われるようになった。

しかし、前述した通り、配線が微細になってくると、バリアメタルの抵抗が無視できなくなってきたため、バリアメタルが不要なメタルを直接加工する方法が浮上してきたというわけである。

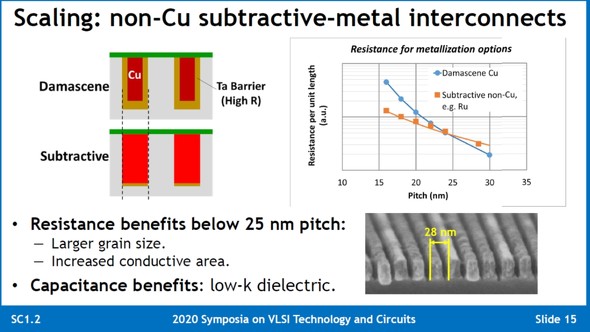

問題は、どのようなメタル材料を選択するかということである。Intelは、その一例として、Ruを直接加工して28nmピッチのメタル配線を形成している。その配線抵抗は、24nmピッチ以下ならば、ダマシン法で形成したCu配線よりも低い値を示している(図11)。

図11:ダマシンで形成したCu配線と直接加工で形成したCu以外の配線(例えばRu) 出典:Mauro Kobrinsky, Intel, “On-Die Interconnect Challenges and Opportunities for Future Technology Nodes”, VLSI 2020, SC1.2(クリックで拡大)

図11:ダマシンで形成したCu配線と直接加工で形成したCu以外の配線(例えばRu) 出典:Mauro Kobrinsky, Intel, “On-Die Interconnect Challenges and Opportunities for Future Technology Nodes”, VLSI 2020, SC1.2(クリックで拡大)Ruは使わない方が良い

しかし、筆者の過去の経験から、Ruを配線材料に使うことはお勧めできない。筆者は、1998年頃、日立製作所のデバイス開発センターで、1GビットDRAMの開発に関わった。そのDRAMでは、キャパシター絶縁膜に(Ba,Sr)TiO2、キャパシター電極にRuを使うことを想定していた。筆者の役目は、Ruピラーの垂直エッチングを行うことであった。筆者は、LamResearchと共同でRu専用エッチャーを開発し、O2とCl2の混合プラズマを用いて、Ruの垂直加工を実現した。

Ruの垂直エッチング自体はそれほど難しくはなかったが、Ruの挙動をコントロールすることが難しかった。Ruは、周辺に酸素があるとRuO2になってしまう。RuO2も導電性を持つため、電気特性には問題がないが、酸素を2個も取り込むため、Ruが膨張してしまうのである。

それでは、最初からRuO2を加工しておけばいいと考え、実行した。ところが、RuO2は還元雰囲気で酸素を放出してしまうのである。その結果、RuO2は穴ぼこだらけのRuになってしまう。

要するに、Ruという材料は、周囲の環境に応じて“呼吸する”のである。こんなメタル材料は、とてもDRAMには使えないと、われわれのグループはキャパシター電極にRuを使うことを放棄した。だから、このような材料は使わない方が良いと思うわけである。

Intelは、現在も10nmのプロセッサの量産がうまくいっていない。その最大の原因は、メタル配線にあると考えている(関連記事:「10nmで苦戦するIntel、問題はCo配線とRuバリアメタルか」)。最初は、M1にダマシン法でCo配線をつくろうとして失敗した模様だ。CoのCMPが不完全で欠陥が除去できなかったからだと推測している。その後は、どうしているのだろうと思っていたら、Ru配線などを検討していたわけか。もしそうなら、Intelの10nmは前途多難と言わざるを得ない。

SynopsysのVictor Moroz氏もまた、1nmにMoを直接加工するメタル配線について発表していた(図12)。個人的な見解では、M1のメタル材料としては、RuよりもMoの方がずっといいと思う。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増