多様な5G要件に対応、柔軟性を備えたXilinx「RF SoC」:フロントエンドをハードIP化

Xilinxは2020年10月27日(米国時間)、5G(第5世代移動通信)基地局向けに「Zynq RF SoC DFE」を発表した。従来品ではソフトIP(Intellectual Property)としてFPGAファブリックに搭載していたデジタルフロントエンド(DFE)機能を、ハードIPとして搭載したことが特長となっている。ハードIP化したことで、演算性能の向上と消費電力の低減を実現した。

デジタルフロントエンドをハードIPとして搭載

Xilinxは2020年10月27日(米国時間)、5G(第5世代移動通信)基地局向けに「Zynq RF SoC DFE」を発表した。

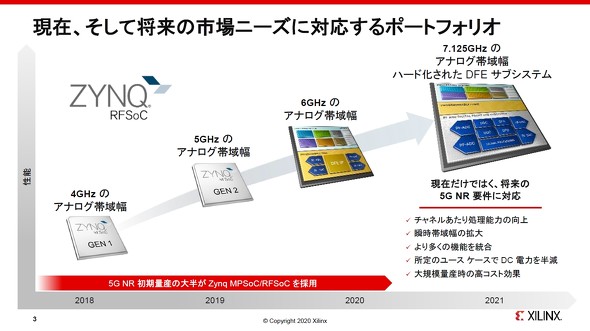

Xilinxは、4G/5G基地局向けにRFデータコンバーターとプログラマブルロジックを統合した「Zynq UltraScale+ RF SoC」を第1世代から第3世代まで展開している(第3世代は2020年11月に量産開始)。これら3つの最大アナログ帯域幅は第1世代が4GHz、第2世代が5GHz、第3世代が6GHz。Zynq RF SoC DFEでは、今後の5Gを見据えて最大アナログ帯域幅を7.125GHzに拡大し、Zynq UltraScale+ RF SoCではソフトIP(Intellectual Property)としてFPGAファブリックに搭載していたデジタルフロントエンド(DFE)機能を、ハードIPとして搭載したことが特長となっている。ハードIP化したことで、演算性能の向上と消費電力の低減を実現した。

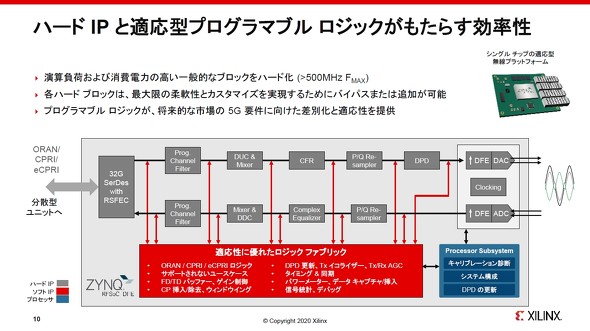

具体的には、RFデータコンバーター(A-Dコンバーター/D-Aコンバーター)、RF信号処理、DUC(デジタルアップコンバーター)、DDC(デジタルダウンコンバーター)、チャネルフィルタリングなどの機能をハードIP化して搭載している。演算負荷が高く、消費電力が大きいフロントエンドの部分をハードIPとしてFPGAファブリックから切り離したことで、FPGAファブリックを、5Gのユースケースに合わせた他の機能の実現に使用できるようになる。

Zynq RF SoC DFEのFPGAファブリックは、ハードIPのブロック一つ一つの入出力にアクセスできるようになっているので、ユースケースや要件に合わせて、必要なハードIPだけで構築することが可能だ。

図の灰色のブロックがハードIP。FPGAファブリック(図の赤い部分)から各ハードIPの入出力にアクセスできるので、必要に応じてハードIPブロックをバイパスしたり追加したりと、柔軟に構成可能だ 出典:Xilinx(クリックで拡大)

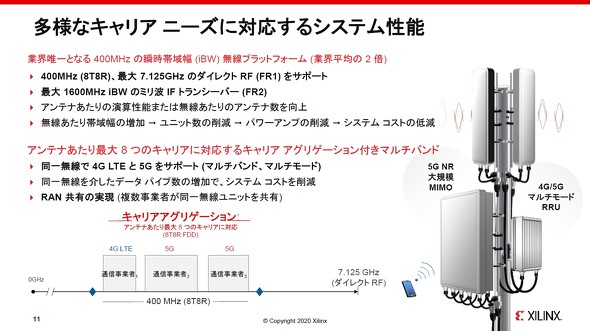

図の灰色のブロックがハードIP。FPGAファブリック(図の赤い部分)から各ハードIPの入出力にアクセスできるので、必要に応じてハードIPブロックをバイパスしたり追加したりと、柔軟に構成可能だ 出典:Xilinx(クリックで拡大)Zynq RF SoC DFEは、最大400MHzの瞬時帯域幅をサポートする他、400MHzのGaNパワーアンプにも対応している。さらに、Zynq RF SoC DFEを搭載したアンテナは、最大8つのキャリアに対応するキャリアアグリゲーション付きマルチバンドをサポート可能だ。

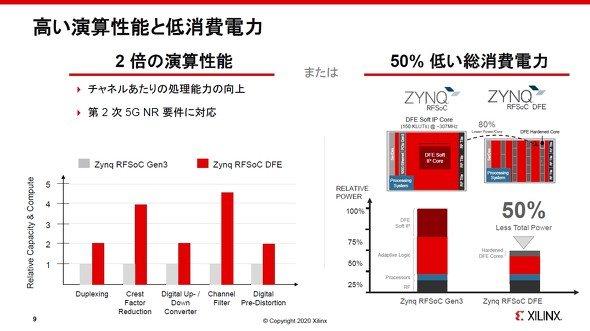

Zynq RF SoC DFEはハードIP化により、既存の第3世代にZynq UltraScale+ RF SoC比べて演算性能が2倍に向上し、消費電力が半減した。

自動車や医療、物流などこれまでにない分野への応用が期待されている5Gでは、ユースケースが多岐にわたる他、無線システムをオープン化するOpen RANの動きも高まっていることから、無線システムでは柔軟性がますます必要になる。XilinxのWWGビジネスでリードシニアディレクターを務めるGilles Garcia氏は、「5G市場では、オペレーターやユーザーからの要求が断片化していくであろうことが予想される。Zynq RF SoC DFEは、そうした要求に応え得る柔軟性の他、システムのコストと消費電力のバランスを最適化できるデバイスだ」と語った。

Zynq RF SoC DFEの出荷は2021年上期を予定している。

関連記事

AMDがXilinxを350億ドルで買収、HPC拡大を狙う

AMDがXilinxを350億ドルで買収、HPC拡大を狙う

AMDは2020年10月27日(米国時間)、Xilinxを350億米ドル(約3兆6500億円)で買収することで合意したと発表した。 5G Open RAN向けのアクセラレーターカード Xilinx

5G Open RAN向けのアクセラレーターカード Xilinx

Xilinxは2020年9月15日(米国時間)、5G(第5世代移動通信)で注目されているオープン無線アクセスネットワーク(Open RAN)向けにテレコムアクセラレーターカード「T1」を発表した。 AIはFPGAのスイートスポット、Xilinxがエッジ推論をデモ

AIはFPGAのスイートスポット、Xilinxがエッジ推論をデモ

Xilinxは、組み込み技術の国際展示会「embedded world 2019」(2019年2月26〜28日、ドイツ・ニュルンベルク)で、自動車や監視カメラなどでの推論、いわゆるエッジデバイスでの推論をイメージしたデモを展示した。 FPGAで“GPU級”のAIアクセラレーター実現を目指す

FPGAで“GPU級”のAIアクセラレーター実現を目指す

AI(人工知能)ソフトウェアを手掛ける新興企業Mipsologyは2020年6月24日(米国時間)、Xilinxのデータセンター向けアクセラレーターカード「Alveo U50」に、Zebraが統合されたと発表した。 サムスン、ザイリンクス製「Versal ACAP」を採用

サムスン、ザイリンクス製「Versal ACAP」を採用

Xilinx(ザイリンクス)によると、Samsung Electronics(サムスン電子)は第5世代移動通信(5G)商用製品に、Xilinx製マルチコアヘテロジニアス演算プラットフォーム「Versal ACAP」を採用した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- パワー停滞も光デバイス堅調、三菱電機の半導体部門

XilinxのGilles Garcia氏

XilinxのGilles Garcia氏