「CXL」がさらに進化、バージョン2.0を発表:データセンター向け高速通信規格(2/2 ページ)

永続性メモリの標準インタフェースに関するWGも設立

また、CXL 2.0規格の全体的なアップデートの一環として、永続性メモリに対する標準インタフェースの提供方法について注力するためのワーキンググループ(WG)が設立された。Carr氏は、「管理用の標準API(Application Programming Interface)を定義することにより、誰もが標準化された方法で永続性メモリをCXL接続ポートに追加できるようになる。CXLを使えば、NVMeと同様に、誰でも独自のメモリ技術を市場に投入して、既存のソフトウェアエコシステムを利用することが可能だ。また、スイッチング機能と組み合わせることにより、メモリの使い方に関する柔軟性を大幅に高められる」と述べている。

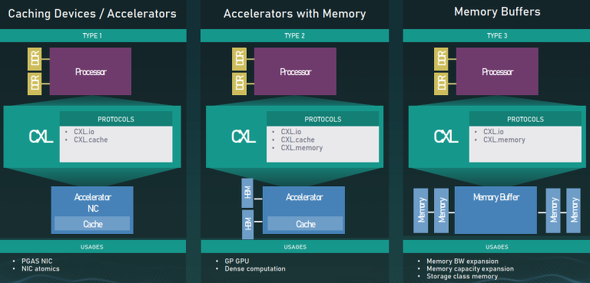

CXLのプロトコルは、「CXL.io」と「CXL.cache」「CXL.memory」の3つに分類することができる。単独で使用できるだけでなく、特定のユースケース向けに組み合わせることも可能だ。これら3つを全て同時に使用する例としては、メモリのアクセラレーターで高性能計算をサポートすることなどが挙げられる。また、メモリバッファの場合は、CXL.ioとCXL.memoryを組み合わせて、メモリ容量拡大やストレージクラスメモリ(SCM)をサポートできる。

CXLが急速に進展し、普及が進んだ背景には、標準規格開発において幅広い業界からのサポートと参加があったという点がある。このため、メモリメーカーとコンポーネントメーカーは従来の枠を超えて、GoogleやIBM、Facebook、Intelなどの大企業を理事会に迎えることができるようになった。中でもIntelは通常、メモリなどの半導体分野において、市場のけん引役とされている。

CXLコンソーシアムのメンバー企業であるMicrochip Technologyは、一番乗りでCXL 2.0対応製品を開発し、最新の低レイテンシPCI Express 5.0(PCIe Gen5)およびCXL 2.0リタイマー「XpressConnect」を発表した。同社のデータソリューション向けプロダクトマーケティング/戦略部門担当マネジャーを務めるAhmad Danesh氏は、「このリタイマーは、全体的なCXL規格と同様に、データセンターワークロードのHPC(High-Performance Computing)需要にも対応可能だ。AI(主に機械学習)などのさまざまな計算ワークロードだけでなく、自動車のADAS(先進運転支援システム)にも必要とされる、超低レイテンシの信号伝送をサポートしているからだ」と述べている。

PCIeリタイマーは通常、ICとしてプリント配線板(PCB)に実装され、PCIeバスを延長することができる。また、インターコネクトやPCB、ケーブル変更などによって断絶が生じた場合に対応することが可能だ。このような断絶が生じると、まるで新しいPCIeデバイスであるかのように、再生信号が両方向に出力されるため、PCIe信号が劣化することになる。

【翻訳:田中留美、編集:EE Times Japan】

関連記事

PCIeの進化が支える次世代インターコネクト技術

PCIeの進化が支える次世代インターコネクト技術

高速バスインタフェース「PCI Express 4.0(PCIe Gen4)」がまさに今、プロセッサ市場に登場しようとしている。しかし、多くの企業は既に、「PCIe 5.0(PCIe Gen5)」が数年以内に登場すると見込んでいるようだ。さらに、「PCIe Gen6」の開発も同時に進められているという。 ハード開発をよりオープンに、団体設立が相次ぐ

ハード開発をよりオープンに、団体設立が相次ぐ

IntelとRISC-Vの支持者たちがそれぞれ、ライバル同士となるアライアンスの設立を発表した。未来のプロセッサを見据え、競合するエコシステムを構築していくという。 「RISC-V」はEmbeddedでマーケットシェアを握れるのか

「RISC-V」はEmbeddedでマーケットシェアを握れるのか

2017年12月に開催された「RISC-V Day 2017 Tokyo」から、著者が注目した4つの講演を紹介する。 光トランシーバーForm Factorの新動向(4) 〜ハイパースケールデータセンターとCPO実用化の行方

光トランシーバーForm Factorの新動向(4) 〜ハイパースケールデータセンターとCPO実用化の行方

前回に続き、光トランシーバーをMulti-Chip Module(MCM)上に実装し、新しい光トランシーバーの市場を開こうとしているCo-Packaged Optics(CPO)実現に向けた課題などを述べる。 SDK「Qiskit」で量子コンピュータの利用を促進

SDK「Qiskit」で量子コンピュータの利用を促進

量子コンピュータでは、アクセスのしやすさと使い勝手の良さを両立した開発環境に対するニーズが高まっている。IBMは量子コンピュータ用のSDK(ソフトウェア開発キット)「Qiskit」によって、ユーザーにとって、量子コンピュータの複雑さが分からなくなるほど容易にプログラミングを行える環境の構築を目指している。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待