「CXL」がさらに進化、バージョン2.0を発表:データセンター向け高速通信規格(1/2 ページ)

オープンな業界標準インターコネクト規格「Compute Express Link(CXL)」が、安定したペースで前進し続けている。今回、始動当初から2年もたたないうちに、次世代版「CXL 2.0」が発表された。CXLコンソーシアムのメンバー企業は既に、このCXL 2.0を適用した製品をリリースしているという。

オープンな業界標準インターコネクト規格「Compute Express Link(CXL)」が、安定したペースで前進し続けている。今回、始動当初から2年もたたないうちに、次世代版「CXL 2.0」が発表された。CXLコンソーシアムのメンバー企業は既に、このCXL 2.0を適用した製品をリリースしているという。

CXL 2.0は、現在既に成熟しているNVMe(Non-Volatile Memory Express)インタフェース規格と同様に、増加し続ける性能需要に対応すべく、旧世代版「CXL 1.0」との後方互換性を維持しながら、新機能を追加したという。CXL 1.0は2019年3月に発表され、同年6月にはCXL 1.1がリリースされている。CXL 2.0へのアップデートが行われた背景にある要因としては、機械学習向けワークロードの需要が増大したために、データセンターアーキテクチャがその対応を迫られ、急速な進化を遂げているということがある。またこの他にも、クラウドコンピューティングや、ネットワークのクラウド化、エッジAI(人工知能)なども挙げられる。

CXLコンソーシアムのディレクターを務めるLarrie Carr氏は、米国EE Timesの取材において、「こうした傾向の中には、データセンターが抱える既存の課題も含まれている。例えば、ヘテロジニアスコンピューティングやサーバのディスアグリゲーション(分離)などの需要が増大していることや、メモリ容量/帯域幅を高める必要性に迫られていることなどがある」と述べる。

CXLは、PCIe物理層で動作する、オープンな業界標準インターコネクトだ。高帯域幅を使用したり、アクセラレーターやメモリバッファ、スマートI/Oデバイスなどのデバイスと、ホストプロセッサとの間の低レイテンシ接続を利用したりすることによって、コヒーレンシ(一貫性)とメモリセマンティクスを実現する。

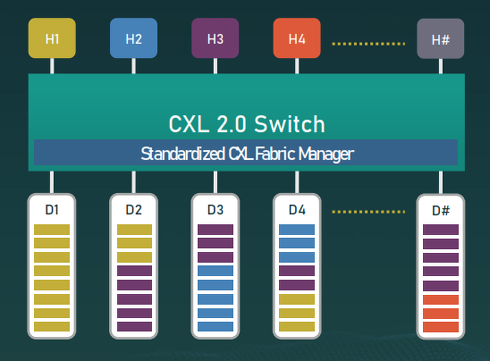

CXL 2.0に追加された機能としては、デバイスのファンアウトやメモリスケーリング、拡張、リソース移動などを実現するためのスイッチングがサポートされている他、メモリプーリングのサポートによってメモリ使用量を最大化し、メモリのオーバープロビジョニングの必要性を制限または排除できるようになっている。さらに、DDRとの同時並行操作を実現しながら、永続性メモリ(パーシステントメモリ)インタフェースを標準管理することにより、他のユーザー向けにDDRを解放することも可能だ。

Carr氏は、「CXL 2.0へのアップデートが実現したことで、メモリ割り当てのコンセプトを介して、16のホストのうちどれか1つにエンドデバイスを簡単に割り当てられるようになった。もし特定のホストにおいて、それ以上エンドデバイスを使用したくない場合、CXLスイッチは、ホットプラグイベントを許可/管理することによって、1つのホストに対してそのデバイスを切断し、他のホストに再度割り当ててメモリプーリングを行えるようにする」と述べる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

「CXL」のロゴ

「CXL」のロゴ