周辺回路とセルアレイを積層して3D NANDの密度をさらに高める:福田昭のストレージ通信(187) アナリストが語る不揮発性メモリの最新動向(14)(1/2 ページ)

今回は、周辺回路とメモリセルアレイを積層することによって3D NANDフラッシュの記憶密度をさらに高める技術を説明する。

メモリセルアレイの下には空き地が広がっていた

フラッシュメモリとその応用に関する世界最大のイベント「フラッシュメモリサミット(FMS:Flash Memory Summit)」が2020年11月10日〜12日に開催された。FMSは2019年まで、毎年8月上旬あるいは8月中旬に米国カリフォルニア州サンタクララで実施されてきた。COVID-19(新型コロナウイルス感染症)の世界的な大流行(パンデミック)による影響で、2020年のFMS(FMS 2020)は開催時期が3カ月ほど延期されるとともに、バーチャルイベントとして開催された。

FMSは数多くの講演と、展示会で構成される。その中で、フラッシュメモリを含めた不揮発性メモリとストレージの動向に関するセッション「C-9: Flash Technology Advances Lead to New Storage Capabilities」が興味深かった。このセッションは4件の講演があり、その中でアナリストによる3件の講演が特に参考になったので、講演の概要をご紹介する。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

本シリーズの第10回から、技術調査会社TechInsightsでシニア技術フェローをつとめるJeodong Choe氏が「Technology Trend:NAND & Emerging Memory(NANDフラッシュメモリと次世代メモリの技術動向)」と題して講演した内容を説明している。第10回は3D NANDフラッシュメモリ(以降は「3D NANDフラッシュ」と略記)各社の開発ロードマップを、第11回は代表的なスマートフォンが搭載してきたNANDフラッシュメモリの変遷を、第12回(前々回)は3D NANDフラッシュ技術の変遷を、第13回(前回)は高層化と多値化、記憶密度の推移を解説した。

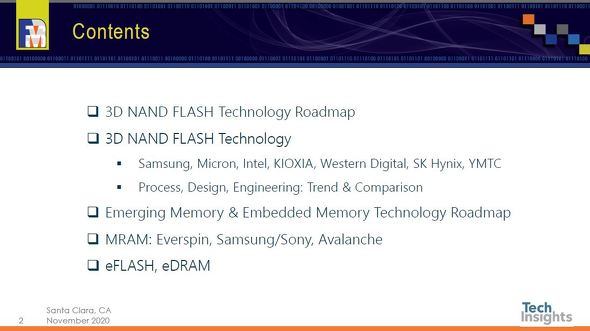

講演のアウトライン。3D NANDフラッシュの開発ロードマップと要素技術、次世代メモリと埋め込みメモリの開発ロードマップなどを解説する。出典:FMS 2020の講演「Technology Trend:NAND & Emerging Memory」の配布資料(クリックで拡大)

講演のアウトライン。3D NANDフラッシュの開発ロードマップと要素技術、次世代メモリと埋め込みメモリの開発ロードマップなどを解説する。出典:FMS 2020の講演「Technology Trend:NAND & Emerging Memory」の配布資料(クリックで拡大)今回は、周辺回路とメモリセルアレイを積層することによって3D NANDフラッシュの記憶密度をさらに高める技術を説明しよう。Micron Technology(Micron)とIntelの連合が初めて製品化し、最近ではSK hynixとYMTCも製品に採用している。

まず前提となるのが、3D NANDフラッシュのメモリセルアレイはシリコンウエハーの表面内部に作り込まれるのではなく、シリコンウエハーの上に成膜技術とエッチング技術によって積み上げられるということだ。プレーナー(2D)NANDフラッシュでは、セルトランジスタのチャンネルと拡散層(ソースとドレイン)をシリコンの表面内部に作り込んでいた。このプロセスそのものは通常のCMOSロジックとあまり変わらない。

ところが3D NANDフラッシュでは、シリコンウエハー表面の上に配線層と絶縁層を交互に成膜し、エッチングによって配線層と絶縁層を貫通する細長い孔を開け、孔の内部に多結晶シリコンのチャンネルを成膜する。このようにして垂直に連なるセルトランジスタを作る。シリコンウエハーの表面内部は触らない。言い換えると、メモリセルアレイの直下にあるシリコンの表面は広大な「空き地」となっている。メモリセルアレイを制御する周辺回路(ペリフェラル)は、メモリセルアレイに隣接してレイアウトしていた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(前編)

- EVに吹く逆風 デンソーの焦りとロームが求める勝機とは

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(後編)

- 石炭灰から「レアアース元素」を回収、新日本繊維【訂正あり】

- 半導体産業を下支え 台湾スタートアップの「3つの特徴」とは

- 「27年度後半の2nm量産誓う」 Rapidus、解析センター開設

- AIと地政学リスクが招く深刻なメモリ危機

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 経産省、Rapidusに6315億円追加支援 「国益のため必ず成功」

- 26年の半導体市場は64%成長で1.3兆ドルに NAND価格は234%上昇