CMOSロジックの高密度化を後押しする次世代の電源配線技術:福田昭のデバイス通信(299) imecが語る3nm以降のCMOS技術(2)(2/2 ページ)

電源/接地線の埋め込みで配線のトラック数をさらに減らす

Myung‐Hee Na氏は講演で、基本セル(スタンダードセル)のトラック数を6トラック(6T)からさらに減らすことの難しさを論じた。例示した基本セルはCMOSインバータ回路である。なお基本セルの縮小を論じるときには、トランジスタ数の最も少ない論理ゲートであるインバータ(論理反転)を扱うことが多い。

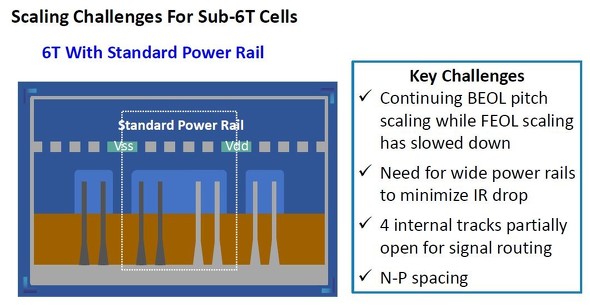

例示したのは、imecのロードマップでは5nmノードに相当する基本セルである。フィン数が2枚のpチャンネルFinFETとnチャンネルFinFETで構成する。セルの高さは6トラック(6T)である。ここからトラック数をさらに減らそうとすると、電源/接地配線を細くしづらい(電気抵抗を上昇させないため)、FinFETの寸法を縮小しづらい、pチャンネルFinFETとnチャンネルFinFETの距離を縮めにくい(素子分離を確保するため)、といった課題が無視できない。

CMOSロジック基本セルの断面構造図(FinFETのフィンおよび最下層金属配線と直交する方向の断面)。セルの高さは6トラック(6T)である。CMOSロジックの密度をさらに高めるためにトラック数を減らそうとすると、いくつもの課題が立ちふさがる。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

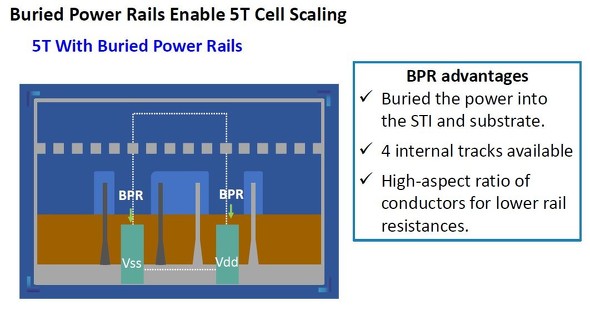

CMOSロジック基本セルの断面構造図(FinFETのフィンおよび最下層金属配線と直交する方向の断面)。セルの高さは6トラック(6T)である。CMOSロジックの密度をさらに高めるためにトラック数を減らそうとすると、いくつもの課題が立ちふさがる。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)この問題を解決する有力な手法が、電源/接地配線を基板側に埋め込むことだ。BPR(Buried Power Rails)と呼ばれる。BPRでトラック数を5トラック(5T)に減らしながらも、信号配線数は6Tと同じ4本を維持できる。BPRの採用による5Tセルは、3nmノードの候補とimecは位置付ける。

セルの高さを5トラック(5T)に下げたCMOSロジック基本セルの断面構造図(FinFETのフィンおよび最下層金属配線と直交する方向の断面)。電源配線と接地配線を基板側に埋め込む(BPR)。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料)

セルの高さを5トラック(5T)に下げたCMOSロジック基本セルの断面構造図(FinFETのフィンおよび最下層金属配線と直交する方向の断面)。電源配線と接地配線を基板側に埋め込む(BPR)。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料)BPRの電源/接地配線はアスペクト比(縦/横比)を高くできるので、電気抵抗を低くしやすい。ただしFinFETのフィン数が1枚に減るので、トランジスタ(FinFET)の電流駆動能力(チャンネル幅当たり)は6Tセルに比べて下がってしまう。トランジスタの密度は上がるものの、性能の低下を抑えるための工夫が必要となる可能性が高い。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説する。 米国のルネサスが販売している8MビットのSTT-MRAM

米国のルネサスが販売している8MビットのSTT-MRAM

今回は、MRAMおよびSTTT-MRAMの開発ベンチャーであるAvalanche Technologyの製品事例を紹介する。 次世代半導体メモリの開発ロードマップ

次世代半導体メモリの開発ロードマップ

今回から、「次世代メモリ(Emerging Memory)」の講演部分を紹介する。 中国の3D NANDフラッシュメーカー「YMTC」の現状

中国の3D NANDフラッシュメーカー「YMTC」の現状

今回は、中国の3D NANDフラッシュベンチャーであるYMTC(Yangtze Memory Technologies Co., Ltd.)の現状に関する講演部分を紹介する。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーは2021年2月3日、2021年3月期(2020年度)第3四半期(2020年10〜12月期)決算を発表するとともに、2020年度通期業績予想を上方修正した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- 次世代パワー半導体 「期待の5材料」の現在地

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「3社のパワー半導体事業を切り出し合弁設立したい」三菱電機社長

- パワー停滞も光デバイス堅調、三菱電機の半導体部門

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼