埋め込み電源配線の構造と材料選択:福田昭のデバイス通信(301) imecが語る3nm以降のCMOS技術(4)(1/2 ページ)

今回は、BPR(Buried Power Rail)の複雑な構造を説明する略語を定義するとともに、金属材料の候補を解説する。

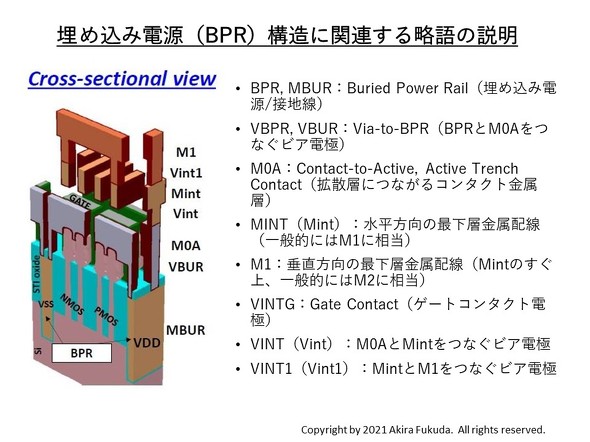

埋め込み電源配線の構造に関連する略語を説明

半導体のデバイス技術とプロセス技術に関する世界最大の国際学会「IEDM(International Electron Devices Meeting)」は、「チュートリアル(Tutorials)」と呼ぶ技術講座を本会議(技術講演会)とは別に、プレイベントとして開催してきた。2020年12月に開催されたIEDM(Covid-19の世界的な流行によってバーチャルイベントとして開催)、通称「IEDM2020」では、合計で6本のチュートリアル講演が実施された。その中で「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」が非常に興味深かった。講演者は研究開発機関のimecでTechnology Solutions and Enablement担当バイスプレジデントをつとめるMyung‐Hee Na氏である。

そこで本講演の概要を本コラムの第298回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの(クリックで拡大)

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの(クリックで拡大)前々回と前回は、3nm世代以降のCMOSロジックで基本セル(スタンダードセル)を縮小するためには、電源/接地配線を基板側に埋め込む技術(BPR:Buried Power Rail)が有力な候補であること、BPRの導入によって電源電圧の降下が大幅に抑えられることを報告した。今回は、BPRの複雑な構造を説明する略語を定義するとともに、金属材料の候補を解説する。

BPR構造のCMOS基本セルは、かなり複雑な構造をしている。複雑な構造を説明するために、いくつかの略語と記号をMyung‐Hee Na氏は講演スライドで使っていた。しかし略語の多くには定義がなかったので、以下の図面で補足説明しておく。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- 加賀電子が新光商事にTOB、完全子会社化へ

- 地政学が変えるメモリ調達戦略 「安く買う」だけでは危険