高耐圧LDMOSの静電破壊耐量と電力効率を両立:車載用アナログIC向け

東芝デバイス&ストレージとジャパンセミコンダクターは2021年6月、車載アナログIC向け高耐圧LDMOSの「静電破壊耐量」と「電力効率」を両立させる技術を開発した。

耐圧80V超のLDMOS、バックゲート比率はHBM耐量に比例せず

東芝デバイス&ストレージとジャパンセミコンダクターは2021年6月、車載アナログIC向け高耐圧LDMOS(Laterally Double Diffused MOS)の「静電破壊耐量」と「電力効率」を両立させる技術を開発したと発表した。

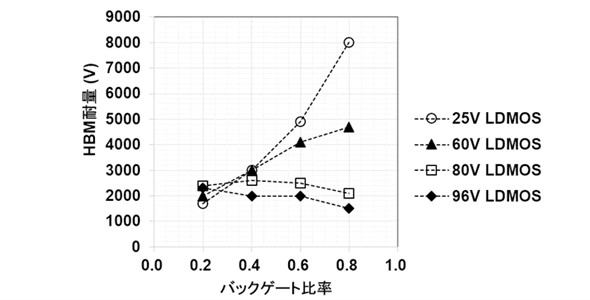

バッグゲート比率(ソース幅とバックゲート幅の合計値に占めるバックゲート幅の割合)を高めていくと、デバイスの横方向に作用する寄生バイポーラ動作が抑制され、HBM(人体帯電モデル)耐量が向上するといわれている。しかし、バックゲート比率を高めるとそれに応じてオン抵抗も増大する。このため、優れたHBM耐量と低オン抵抗を両立させることは難しいといわれてきた。

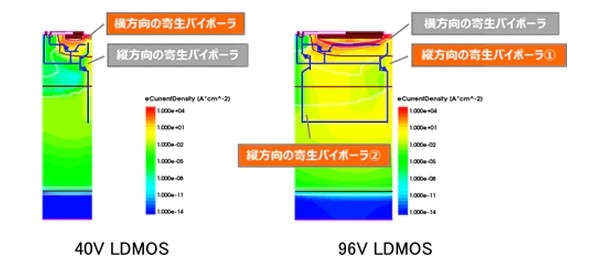

両社は今回、複数の耐圧でLDMOSのHBM耐量を評価し、デバイスの動作をシミュレーションした。この結果、40Vの低耐圧では横方向の寄生バイポーラ動作が支配的となる。これに対し96Vの高耐圧では、横方向に加え縦方向にも寄生バイポーラが有効に動作するため、バッグゲート比率はHBM耐量に比例しないことが分かった。このことから、バックゲート比率を高めずに、HBM耐量を向上させられるという。

耐圧80V以上のLDMOSを搭載したアナログICは主に、電動パワーステアリングやエンジンの制御などに用いられているという。東芝デバイス&ストレージは、今回開発したLDMOS以外でも、さまざまな耐圧や用途に向けたLDMOSを用意している。高耐圧アナログICに車載向け不揮発性メモリを混載(eNVM)した第5世代プロセス製品も既に開発中だという。

関連記事

東芝、ソリッドステートLiDAR向け受光技術を開発

東芝、ソリッドステートLiDAR向け受光技術を開発

東芝は、「ソリッドステート式LiDAR」向けの受光技術と実装技術を新たに開発した。新技術を採用すると、200mの最長測定距離を維持しつつ、従来に比べサイズが3分の1で、解像度は4倍となるLiDARを実現できるという。 東芝、トリプルゲートIGBTとゲート制御技術を開発

東芝、トリプルゲートIGBTとゲート制御技術を開発

東芝は、スイッチング損失を全体で最大40.5%も低減できる「トリプルゲートIGBT」を開発した。再生可能エネルギーシステムや電気自動車(EV)などに搭載される電力変換器の高効率化に向けて、早期実用化を目指す。 量子技術の産業化を加速、日本企業11社が協議会設立

量子技術の産業化を加速、日本企業11社が協議会設立

東芝、富士通、トヨタ自動車などの民間企業11社は2021年5月31日、量子技術の研究開発と社会実装の加速を目指す協議会「量子技術による新産業創出協議会」の設立発起人会を開催した。 東芝、SiCモジュール向けパッケージ技術を開発

東芝、SiCモジュール向けパッケージ技術を開発

東芝デバイス&ストレージは、SiC(炭化ケイ素)モジュール向けパッケージ技術を開発したと発表した。従来のパッケージ技術に比べ、面積を約20%削減でき、製品の信頼性は2倍に向上するという。 東芝、保護機能を強化した電子ヒューズを追加

東芝、保護機能を強化した電子ヒューズを追加

東芝デバイス&ストレージは、繰り返し使える電子ヒューズ(eFuse IC)の新製品として、保護機能を強化した「TCKE712BNL」を追加し、出荷を始めた。 東芝、ボタンにも内蔵できるBLEモジュール開発

東芝、ボタンにも内蔵できるBLEモジュール開発

東芝は、衣服のボタンにも内蔵できる小型の「Bluetooth low energy(BLE)モジュール」を開発、サンプル出荷を始める。独自のSASP(Slot Antenna on Shielded Package)技術を用いて実現した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

HBM耐量とバックゲート比率の関係性 出典:東芝デバイス&ストレージ

HBM耐量とバックゲート比率の関係性 出典:東芝デバイス&ストレージ 耐圧によって寄生バイポーラ動作の違いを示すESDシミュレーション結果 出典:東芝デバイス&ストレージ

耐圧によって寄生バイポーラ動作の違いを示すESDシミュレーション結果 出典:東芝デバイス&ストレージ