産総研、超伝導量子アニーリングマシンを開発:独自のアーキテクチャを採用

産業技術総合研究所(産総研)は、超伝導量子アニーリングマシンの開発と動作実証に成功した。従来方式に比べ1桁少ない量子ビット数で、組み合わせ最適化問題を解くことが可能になるという。

従来に比べ1桁少ない量子ビット数で、組み合わせ最適化問題を解く

産業技術総合研究所(産総研)新原理コンピューティング研究センターの川畑史郎総括研究主幹らは2021年7月、デバイス技術研究部門と共同で、超伝導量子アニーリングマシンの開発と動作実証に成功したと発表した。従来方式に比べ1桁少ない量子ビット数で、組み合わせ最適化問題を解くことが可能になるという。

量子アニーリングは、組み合わせ最適化問題をイジング模型の最小エネルギー状態探索問題に変換し、量子力学的重ね合わせを制御して近似解を求める手法である。カナダのベンチャー企業であるD-Wave Systems社は、2011年に超伝導量子ビットとグラフ埋め込み技術を利用した量子アニーリングマシンを商用化。2020年には5000量子ビット級の製品販売を始めている。

ところが、グラフ埋め込み技術を用いた従来の量子アニーリングマシンは、量子ビットのコピーを大量に用意する必要があり、大規模な組み合わせ最適化問題を扱えない、という課題があった。

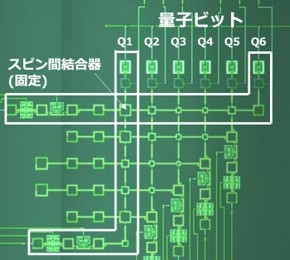

産総研はこれまで、超伝導量子アニーリングマシンと超伝導量子コンピュータのハードウエア設計や製造、評価基盤技術の確立および、社会実装へ向けた研究開発に取り組んできた。そして、特定の最適化問題に特化した量子アニーリングマシンのアーキテクチャ(ASAC)を初めて提唱。これに基づき、古典2ビット乗算回路専用の超伝導量子アニーリングマシン(6量子ビット)を設計、製造した。

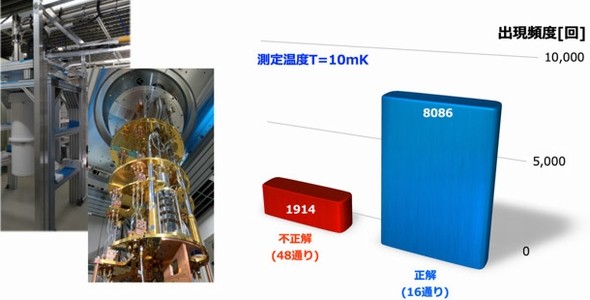

古典2ビット乗算回路の場合、解候補は64通り(26)あるが、この中で正解(正常動作)は16通り(24)だけである。10mKという極低温評価システムでの実験結果によれば、1万回の測定を行い80%以上の正答率が得られることを確認した。

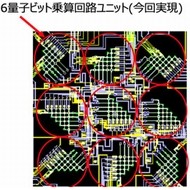

産総研が提唱するASACを用いることで、必要最小限の量子ビット数で大規模な組み合わせ最適化問題を解くことが可能となる。冗長量子ビットの数は、グラフ埋め込み方式に比べ1桁少なくすることができるという。しかも、さまざまな組み合わせ最適化問題にも適応可能なアーキテクチャである。

産総研は今後、大規模な量子アニーリングマシンを製造し、極低温環境での動作実証を行い、ASAC方式の優位性を実証していく予定だ。また、実用化に向けて正答率をさらに高めていく。そのために必要となるノイズ低減技術や高品質量子ビット製造技術などの開発に取り組んでいく。

関連記事

次世代有機LED材料における電子の動きを直接観察

次世代有機LED材料における電子の動きを直接観察

筑波大学や高エネルギー加速器研究機構(KEK)、産業技術総合研究所(産総研)および、九州大学らの研究チームは、次世代の有機LED(OLED)材料として注目される熱活性型遅延蛍光(TADF)について、電子の動きを直接観察することに成功し、発光効率が低下する原因を突き止めた。 量子センサーのスピン情報、電気的読み出しに成功

量子センサーのスピン情報、電気的読み出しに成功

東京工業大学と産業技術総合研究所(産総研)の共同研究グループは、ダイヤモンド量子センサーのスピン情報を、電気的に読み出すことに成功した。感度が高い集積固体量子センサーの実現が期待される。 産総研、空気中の湿度変化で発電する電池を開発

産総研、空気中の湿度変化で発電する電池を開発

産業技術総合研究所(産総研)は、空気中の湿度変化を利用して発電する「湿度変動電池」を開発した。溶液からなる素子のため内部抵抗が極めて小さく、mAレベルの電流を連続して取り出すことに成功した。 MRAM用単結晶MTJ素子を300mmウエハー上に作製

MRAM用単結晶MTJ素子を300mmウエハー上に作製

産業技術総合研究所(産総研)は、MRAM用の単結晶MTJ(磁気トンネル接合)素子をシリコンLSIに集積化するための3次元積層プロセス技術を開発した。 産総研、SiCモノリシックパワーICの開発に成功

産総研、SiCモノリシックパワーICの開発に成功

産業技術総合研究所(産総研)は、SiC(炭化ケイ素)半導体を用い、縦型MOSFETとCMOS駆動回路をワンチップに集積したSiCモノリシックパワーICを開発、そのスイッチング動作を確認した。SiCモノリシックパワーICを実現したのは世界で初めてという。 産総研ら、CNTシリコーンゴム複合材料を開発

産総研ら、CNTシリコーンゴム複合材料を開発

産業技術総合研究所(産総研)は、導電性や柔軟性、耐久性に優れた「CNTシリコーンゴム複合材料」を日本ゼオンと共同で開発したと発表した。医療用ウェアラブル機器向け電極パッドなどの用途に提案していく。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

古典2ビット乗算回路専用の超伝導量子アニーリングマシン(6量子ビット)の顕微鏡写真 出典:産総研

古典2ビット乗算回路専用の超伝導量子アニーリングマシン(6量子ビット)の顕微鏡写真 出典:産総研 10mKの極低温性能評価システムと2ビット乗算回路専用量子アニーリングマシン(6量子ビット)の10mKにおける実験結果 出典:産総研

10mKの極低温性能評価システムと2ビット乗算回路専用量子アニーリングマシン(6量子ビット)の10mKにおける実験結果 出典:産総研 今回開発した乗算回路ユニット(6量子ビット)をタイル状につなぎ合わせた、6ビット乗算回路専用超伝導量子アニーリングマシン(78量子ビット)の予想図 出典:産総研

今回開発した乗算回路ユニット(6量子ビット)をタイル状につなぎ合わせた、6ビット乗算回路専用超伝導量子アニーリングマシン(78量子ビット)の予想図 出典:産総研