産総研、SiCモノリシックパワーICの開発に成功:縦型MOSFETとCMOSを1チップに

産業技術総合研究所(産総研)は、SiC(炭化ケイ素)半導体を用い、縦型MOSFETとCMOS駆動回路をワンチップに集積したSiCモノリシックパワーICを開発、そのスイッチング動作を確認した。SiCモノリシックパワーICを実現したのは世界で初めてという。

「p型MOSFETの出力電流増大」と「高電圧絶縁」を同時に達成

産業技術総合研究所(産総研)は2021年5月、SiC(炭化ケイ素)半導体を用い、縦型MOSFETとCMOS駆動回路をワンチップに集積したSiCモノリシックパワーICを開発、そのスイッチング動作を確認したと発表した。SiCモノリシックパワーICを実現したのは世界で初めてという。

産総研はこれまで、独自構造のSiC縦型パワーMOSFETとして、IE-MOSFET(Implantation&Epitaxial MOSFET)やIE-UMOSFET(Implantation&Epitaxial Trench MOSFET)を開発してきた。また、駆動回路として用いるSiC CMOSの要素技術開発や、SiCパワーデバイスを用いたスイッチング技術の研究などにも取り組んできた。今回はこれらの研究成果を結集した。

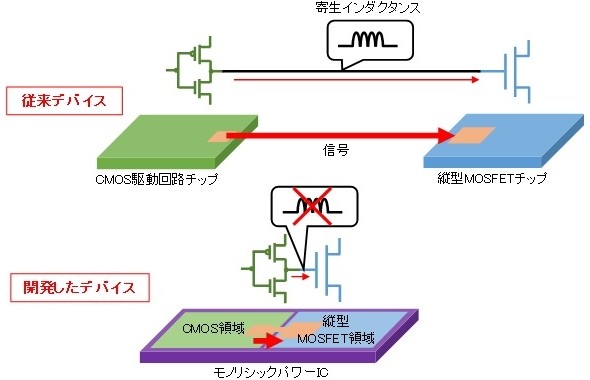

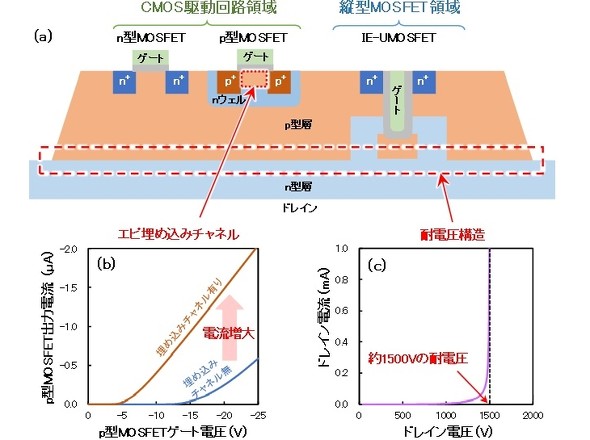

開発したSiCモノリシックパワーICは、ワンチップ上にIE-UMOSFETとSiC CMOS駆動回路を集積している。縦型MOSFETとして採用したIE-UMOSFETは、表面に設けた溝の側壁に半導体領域(チャネル)を形成した構造で、オン状態での抵抗を大幅に低減したという。CMOS駆動回路はIE-UMOSFETと共通のp型層上に形成した。

こうした構成にすることで、「p型MOSFETの出力電流増大」と「高電圧絶縁」を同時に達成した。一般的なSiC CMOSは、p型MOSFETの出力電流がn型MOSFETの出力電流より大きく劣る。今回用いたIE-UMOSFETは、p型層が結晶品質の高いエピタキシャル膜で形成されており、製造プロセスをほとんど変更せずに、エピ埋め込みチャネルを作り込むことができたという。この結果、p型MOSFETの出力電流を従来の4倍に増やすことができた。

IE-UMOSFETと共通の耐電圧構造内にSiC CMOSを形成することで、CMOS駆動回路を1500Vのドレイン電圧から絶縁している。このために新たな製造プロセスを追加する必要もないという。

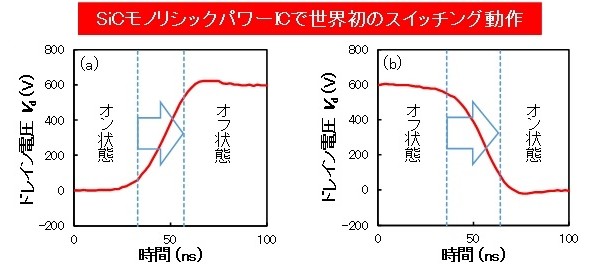

試作したSiCモノリシックパワーICを、ドレイン電圧600V、ドレイン電流10Aでスイッチング動作させ、「ターンオフ」および、「ターンオン」の動作波形を確認した。これにより、SiCモノリシックパワーICによるスイッチング動作を世界で初めて実証した。

産総研は今後、SiC CMOS駆動回路の出力電流をさらに大きくし、SiCモノリシックパワーICの高速スイッチングを目指す。さらに、センサーやロジック回路などの集積化にも取り組む予定である。

今回の研究成果は、産総研先進パワーエレクトロニクス研究センターパワーデバイスチームの岡本光央主任研究員や原田信介研究チーム長、パワー回路集積チームの八尾惇研究員、佐藤弘研究チーム長らによるものである。

関連記事

産総研ら、CNTシリコーンゴム複合材料を開発

産総研ら、CNTシリコーンゴム複合材料を開発

産業技術総合研究所(産総研)は、導電性や柔軟性、耐久性に優れた「CNTシリコーンゴム複合材料」を日本ゼオンと共同で開発したと発表した。医療用ウェアラブル機器向け電極パッドなどの用途に提案していく。 複数AIアクセラレーター搭載の評価チップを試作

複数AIアクセラレーター搭載の評価チップを試作

新エネルギー・産業技術総合開発機構(NEDO)と産業技術総合研究所(産総研)および、東京大学は共同で、仕様が異なる6種類のAIアクセラレーターを搭載した評価チップ「AI-One」を設計、試作を始めた。これを活用すると、短い期間で安価にAIチップの設計と評価が可能になる。 産総研、仮想実験環境で材料の電気的特性を予測

産総研、仮想実験環境で材料の電気的特性を予測

産業技術総合研究所(産総研)は、第一原理計算シミュレーターとAI技術を連携させることで、実験データと同等の電気伝導度を計算する基盤技術を開発した。研究成果を用いると、材料の開発期間を大幅に短縮できる可能性がある。 東京大、高い伝導特性を有する導電性高分子を開発

東京大、高い伝導特性を有する導電性高分子を開発

東京大学らの研究グループは、従来に比べ高い結晶性と伝導特性を有する導電性高分子を開発した。これまでより酸化力が強いラジカル塩ドーパントを独自開発し、これを高分子半導体に作用させることで実現した。 NIMS、Mg3Sb2系材料で高い熱電変換性能を実現

NIMS、Mg3Sb2系材料で高い熱電変換性能を実現

物質・材料研究機構(NIMS)は、n型Mg3Sb2系材料に、わずかな銅原子を添加することで熱伝導率を大きく低減し、同時に高い電荷移動度を実現することに成功した。この材料を用いて試作した熱電モジュールは、希少元素のTeを用いたBi2Te3系材料に匹敵する熱電変換効率が得られたという。 ナノすりガラス、nm級凹凸加工で超親水性を実現

ナノすりガラス、nm級凹凸加工で超親水性を実現

東京大学らの研究グループは、ナノメートル級の凹凸を設けた「ナノすりガラス」を開発した。ナノすりガラスの表面は、150℃という高温でも長時間にわたって超親水性を維持することができ、有機半導体でも良質な単結晶膜を大きな面積で製造することが可能だという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

開発したモノリシックパワーIC技術の概念図 出典:産総研

開発したモノリシックパワーIC技術の概念図 出典:産総研

開発したモノリシックパワーICのスイッチング動作波形 出典:産総研

開発したモノリシックパワーICのスイッチング動作波形 出典:産総研