次々世代のトランジスタ「シーケンシャルCFET」でシリコンの限界を突破(後編):福田昭のデバイス通信(315) imecが語る3nm以降のCMOS技術(18)(1/2 ページ)

後編となる今回は、「シーケンシャル(Sequential)CFET」の具体的な試作例を紹介する。

GeのpチャンネルMOSでCMOSロジックの性能を向上

【ご注意】今回は前編の続きです。まず前編を読まれることを推奨します。

前編では、「シーケンシャル(Sequential)CFET」がボトム側とトップ側で異なるトランジスタ材料が選べることと、その利点を説明した。後編では、その具体的な試作例を紹介しよう。

imecが講演でふれたのは、いずれも、Intelが試作したシーケンシャルCFETの発表事例である。発表は2件あり、1件はnチャンネルSi(シリコン)とpチャンネルGe(ゲルマニウム)のCFET、もう1件はnチャンネルGaN(窒化ガリウム)とpチャンネルSiのCFETとなっている。発表があったのはいずれも、2019年12月に米国サンフランシスコで開催された国際学会IEDMである。

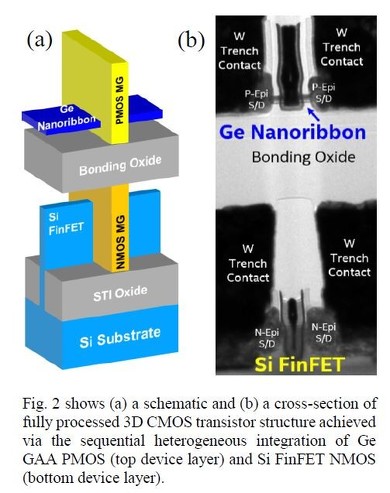

まずは始めの1件の概要を説明する。ボトム側がnチャンネルSi FinFET、トップ側がpチャンネルGeナノリボン(ナノシート)構造FETとなっている。Geトランジスタ用のGeチャンネル層は、Siウエハーにバッファ層を介してエピタキシャル成長させた。

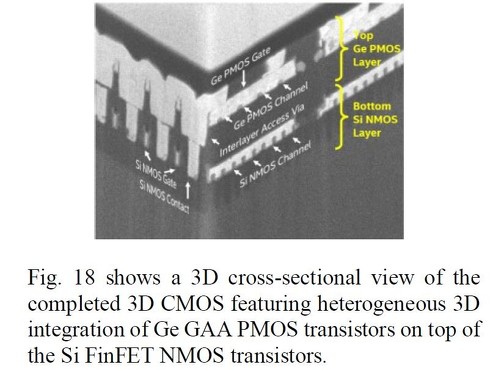

ボトム側がnチャンネルSi FinFET、トップ側がpチャンネルGeナノリボン(ナノシート)構造FETのシーケンシャルCFET。左は構造図。右は試作したCFETの断面を電子顕微鏡によって観察した画像。出典:intelが2019年12月に国際学会IEDMで発表した論文「300mm Heterogeneous 3D Integration of Record Performance Layer Transfer Germanium PMOS With Silicon NMOS For Low Power High Performance Logic Applications」(論文番号29.7)から(クリックで拡大)

ボトム側がnチャンネルSi FinFET、トップ側がpチャンネルGeナノリボン(ナノシート)構造FETのシーケンシャルCFET。左は構造図。右は試作したCFETの断面を電子顕微鏡によって観察した画像。出典:intelが2019年12月に国際学会IEDMで発表した論文「300mm Heterogeneous 3D Integration of Record Performance Layer Transfer Germanium PMOS With Silicon NMOS For Low Power High Performance Logic Applications」(論文番号29.7)から(クリックで拡大)製造工程は以下のように進む。まず、直径300mmのSiウエハー(「デバイスウエハー」とIntelは呼称)にnチャンネルMOSのFinFETを作り込む。続いてウエハー貼り合わせ用の酸化膜をウエハー表面に成膜する。一方で別のSiウエハー(「ドナーウエハー」とIntelは呼称)にGe層を成膜しておく。

そしてデバイスウエハーとドナーウエハーを貼り合わせる。続いてドナーウエハーの大部分をへき開によって取り除く。Ge層を適切な厚みまで薄くして洗浄し、ナノリボン(ナノシート)構造とゲート電極を作り込む。それからボトム側とトップ側を結線するためのコンタクトとビアを形成する。

シーケンシャルCFETの製造工程フロー。出典:intelが2019年12月に国際学会IEDMで発表した論文「300mm Heterogeneous 3D Integration of Record Performance Layer Transfer Germanium PMOS With Silicon NMOS For Low Power High Performance Logic Applications」(論文番号29.7)から(クリックで拡大)

シーケンシャルCFETの製造工程フロー。出典:intelが2019年12月に国際学会IEDMで発表した論文「300mm Heterogeneous 3D Integration of Record Performance Layer Transfer Germanium PMOS With Silicon NMOS For Low Power High Performance Logic Applications」(論文番号29.7)から(クリックで拡大)直径300mmのウエハー貼り合わせによって試作したシーケンシャルCFETのGeトランジスタは、これまでに試作されたGeトランジスタと比べて高い伝達コンダクタンス(飽和値)と低いオフ電流を示した。またGe層の正孔(ホール)移動度はSi層の約3倍と高くなった。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待