次々世代のトランジスタ「シーケンシャルCFET」でシリコンの限界を突破(前編):福田昭のデバイス通信(314) imecが語る3nm以降のCMOS技術(17)

今回と次回は「シーケンシャル(Sequential)CFET」の重要な特徴である、ボトム側とトップ側で異なるトランジスタ材料が選べることの利点と、実際にCFETを試作した事例を解説する。

ボトム側とトップ側で異なるトランジスタ材料を選べる

半導体のデバイス技術とプロセス技術に関する世界最大の国際学会「IEDM(International Electron Devices Meeting)」は、「チュートリアル(Tutorials)」と呼ぶ技術講座を本会議(技術講演会)とは別に、プレイベントとして開催してきた。2020年12月に開催されたIEDM(Covid-19の世界的な流行によってバーチャルイベントとして開催)、通称「IEDM2020」では、合計で6本のチュートリアル講演が実施された。その中で「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」が非常に興味深かった。講演者は研究開発機関のimecでTechnology Solutions and Enablement担当バイスプレジデントをつとめるMyung‐Hee Na氏である。

そこで本講座の概要を本コラムの第298回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

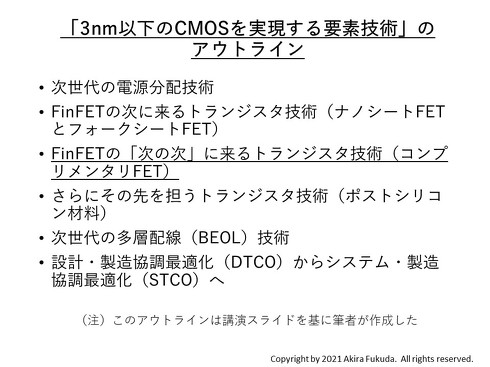

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。本シリーズの第11回から「FinFETの「次の次」に来るトランジスタ技術(コンプリメンタリFET)」の講演部分を紹介している(クリックで拡大)

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。本シリーズの第11回から「FinFETの「次の次」に来るトランジスタ技術(コンプリメンタリFET)」の講演部分を紹介している(クリックで拡大)本シリーズの第11回から、3番目のパートである「FinFETの「次の次」に来るトランジスタ技術(コンプリメンタリFET)」の講演部分を紹介している。「コンプリメンタリFET(C(Complementary)FET)」は、製造方法の違いによって2種類に分けられる。1つはボトム側のトランジスタとトップ側のトランジスタをモノリシック集積する「モノリシック(Monolithic)CFET」である。第14回では、このモノリシックCFETの製造プロセスを簡単に説明した。そして前々回(第15回)と前回(第16回)では、もう1つのCFETである、ボトム側のトランジスタとトップ側のトランジスタをウエハーの貼り合わせによって形成する「シーケンシャル(Sequential)CFET」の製造プロセスと課題を解説した。

今回と次回は「シーケンシャル(Sequential)CFET」の重要な特徴である、ボトム側とトップ側で異なるトランジスタ材料が選べることの利点と、実際にCFETを試作した事例を紹介しよう。

シリコン(Si)を超える性能を別の高性能材料で引き出す

シーケンシャルCFETはウエハーの貼り合わせによって製造する。ウエハーの一部はMOSFETのチャンネル部分となる。ボトム側とトップ側で異なる材料のウエハーを使えば、異なる材料をチャンネルとするCFETを作れる。材料の選択によっては、従来のシリコンCMOSを超える性能のCMOS(CFET)を実現できる。

シリコン(Si)のトランジスタと、別の材料によるトランジスタを組み合わせたコンプリメンタリFET(C(Complementary)FET)の試作例。左はボトム側にnチャンネルのSi FinFET、トップ側にpチャンネルのゲルマニウム(Ge)ナノリボン(ナノシート)構造を選択したCFET。右はボトム側にnチャンネルのSi MOSFET、トップ側にpチャンネルの窒化ガリウム(GaN) MOSFETを選択したCFET。いずれもintelが試作して国際学会IEDM(IEDM 2019)で発表したもの。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料)

シリコン(Si)のトランジスタと、別の材料によるトランジスタを組み合わせたコンプリメンタリFET(C(Complementary)FET)の試作例。左はボトム側にnチャンネルのSi FinFET、トップ側にpチャンネルのゲルマニウム(Ge)ナノリボン(ナノシート)構造を選択したCFET。右はボトム側にnチャンネルのSi MOSFET、トップ側にpチャンネルの窒化ガリウム(GaN) MOSFETを選択したCFET。いずれもintelが試作して国際学会IEDM(IEDM 2019)で発表したもの。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料)例えば、シリコン(Si)はキャリア移動度の非対称性が大きい。伝導電子(エレクトロン)の移動度はかなり高いのに対し、正孔(ホール)の移動度が低い。言い換えると、nチャンネルMOSに比べるとpチャンネルMOSの性能が低い。このため、従来のトランジスタ技術ではpチャンネルMOSに歪みシリコン技術を積極的に導入することで、正孔(ホール)の移動度を高めている。

これに対してシーケンシャルCFETでは、pチャンネルMOSのチャンネル材料にゲルマニウム(Ge)を選択することで、CMOSデバイスの性能を高められる。ゲルマニウム(Ge)の正孔(ホール)移動度は、Siよりも大幅に高いからだ。

また化合物半導体の窒化ガリウム(GaN)は、伝導電子(エレクトロン)の移動度がシリコン(Si)に比べて高く、パワーデバイスとしての性能指数がnチャンネルだとSiよりもはるかに高い。そこでnチャンネルMOSの材料をGaNに変更し、pチャンネルMOSのSiと組み合わせると、高周波用途とパワー用途に適したCMOSデバイスを実現できる。

(後編に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

ルネサス、供給確保で21年7〜9月期売上高2400億円目指す

ルネサス、供給確保で21年7〜9月期売上高2400億円目指す

ルネサス エレクトロニクスは2021年7月29日、2021年12月期第2四半期(4〜6月)業績(Non-GAAPベース)を発表した。第2四半期3カ月間の売上高は2179億円で前年同期比30.7%増、営業利益は614億円で同2.03倍と大幅な増収増益になった。売上総利益率は52.0%、営業利益率は28.2%だった。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説する。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

今回は「強誘電体メモリ(FeRAM)」を取り上げる。FeRAMの記憶原理と、60年以上に及ぶ開発の歴史を紹介しよう。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk