「システム・製造協調最適化(STCO)」の実現技術(後編):福田昭のデバイス通信(327) imecが語る3nm以降のCMOS技術(30)(1/2 ページ)

本シリーズの最終回となる今回は、前回に続き「システム・製造協調最適化(STCO)」を解説する。

(ご注意)今回は前編の続きです。まず前編を読まれることを推奨します。

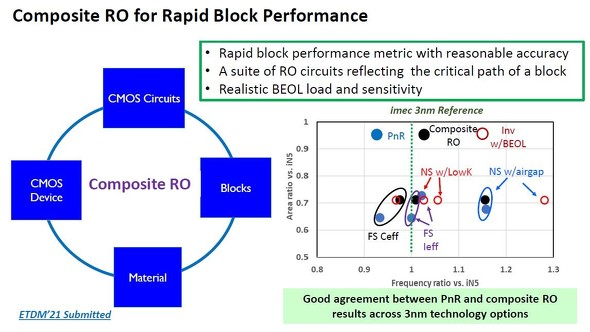

回路ブロックの消費電力と動作周波数を素早く見積もりたい

前編では、7nm世代以降の技術ノードでは「設計・製造協調最適化(DTCO:Design Technology Co-Optimization)」技術だけでは「消費電力と性能、シリコン面積(PPA:Power、Performance、Area)」の最適化が徐々に難しくなることを述べた。DTCOはCMOSロジックのトランジスタや基本セル(スタンダードセル)などの最適化に役立つ。

7nm世代以降では、回路ブロックやサブシステムなどでも最適化の条件をあらかじめ見積もっておくことが望ましい。将来の3nm世代では、回路ブロックをあらかじめ最適化することが必須になる。その手段として考案されているのが、回路ブロックやサブシステムなどを最適化する手法「システム・製造協調最適化(STCO:System Technology Co-Optimization)」である。短時間かつ高精度で回路ブロックの消費電力と性能(動作周波数)を推定できるようになる。

前編で述べたように、回路ブロックの消費電力と性能(動作周波数)をあらかじめ見積もる従来手法は大別すると2つある。1つは高精度だが時間がかかる手法、すなわち回路ブロックのマスクレイアウト設計(配置配線(PnR)設計)を完了させてから、回路ブロックの消費電力と性能を推定する手法だ。もう1つは、時間はかからないものの精度が低い手法、すなわちリング発振器(RO)をモニター回路とする回路シミュレーションから回路ブロックの消費電力と性能を推定する手法である。

回路ブロックの影響を考慮したリング発振器をモデル化

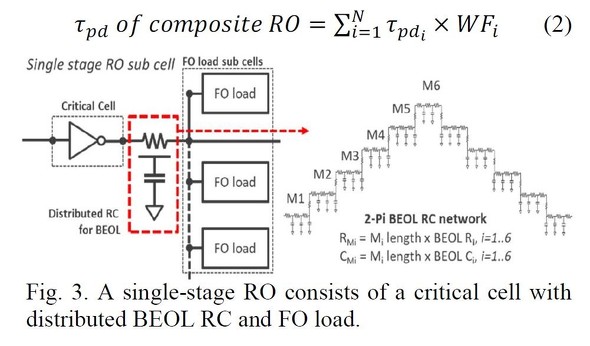

上記の課題に対してimecは、「コンポジットリング発振器(Composite RO)」と呼ぶ特殊なリング発振器をモニター回路に利用することで、迅速かつ高い精度で回路ブロックの消費電力と動作周波数を推定することを試みた。1個のリング発振器は19段のインバータ閉回路で構成する。各段では、6層の金属配線を2πネットワーク状に接続したRC線路の負荷モデルをインバータの直後に接続してある。

「コンポジットリング発振器(Composite RO)」の構造。1段(single-stage)分だけを図示している(左)。6層金属配線(M1〜M6)の負荷を2πネットワークのRC線路でモデル化した(右)。さらに、ファンアウト(FO)の負荷を組み込んでいる[クリックで拡大] 出所:imec(2021年4月に開催された国際学会「2021 Electron Device Technology and Manufacturing Conference(EDTM)でimecが発表した論文「Disruptive Technology Elements, and Rapid and Accurate Block-Level Performance Evaluation for 3nm and Beyond」)

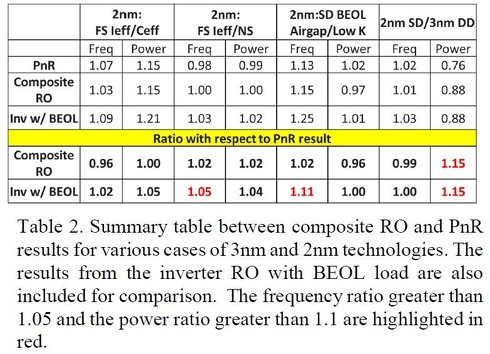

「コンポジットリング発振器(Composite RO)」の構造。1段(single-stage)分だけを図示している(左)。6層金属配線(M1〜M6)の負荷を2πネットワークのRC線路でモデル化した(右)。さらに、ファンアウト(FO)の負荷を組み込んでいる[クリックで拡大] 出所:imec(2021年4月に開催された国際学会「2021 Electron Device Technology and Manufacturing Conference(EDTM)でimecが発表した論文「Disruptive Technology Elements, and Rapid and Accurate Block-Level Performance Evaluation for 3nm and Beyond」)コンポジットリング発振器をモデルとするシミュレーションによって動作周波数と消費電力を推定し、配置配線(PnR)設計完了後のシミュレーション結果(基準値)および、通常のリング発振器(金属配線の負荷付き)をモデルとするシミュレーション結果と比較した。CMOSロジックを構成する要素技術には2nm世代のフォークシート(FS)構造、2nm世代のナノシート(NS)構造、2nm世代のエアギャップ絶縁と低誘電率(Low K)絶縁、3nm世代のデュアルダマシン(DD)、2nm世代のセミダマシン(SD)を選び、要素技術の違いによる動作周波数と消費電力の変化を推定した。

配置配線(PnR)設計完了後のシミュレーション結果を基準値(1.00)とすると、通常のリング発振器(金属配線の負荷付き)をモデルとするシミュレーション結果に比べ、コンポジットリング発振器をモデルとするシミュレーション結果は基準値にかなり近かかった。

要素技術の違いによる動作周波数と消費電力の変化(シミュレーションによる推定)。項目は左から、2nm世代のフォークシート(FS)構造における電流(速度)優先設計(FS Ieff)と容量(低消費電力)優先設計(FS Ceff)の比較、2nm世代のフォークシート(FS)構造(電流優先設計)とナノシート(構造)の比較、2nm世代のセミダマシン配線におけるエアギャップ絶縁と低誘電率(Low K)絶縁の比較、2nm世代のセミダマシン配線と3nm世代のデュアルダマシン配線の比較、である。数値の赤字は、基準値である配置配線(PnR)後のシミュレーション結果とのズレが動作周波数で1.05以上、消費電力で1.10以上に達した場合(差異が大きい場合)[クリックで拡大] 出所:imec(2021年4月に開催された国際学会「2021 Electron Device Technology and Manufacturing Conference(EDTM)でimecが発表した論文「Disruptive Technology Elements, and Rapid and Accurate Block-Level Performance Evaluation for 3nm and Beyond」から)

要素技術の違いによる動作周波数と消費電力の変化(シミュレーションによる推定)。項目は左から、2nm世代のフォークシート(FS)構造における電流(速度)優先設計(FS Ieff)と容量(低消費電力)優先設計(FS Ceff)の比較、2nm世代のフォークシート(FS)構造(電流優先設計)とナノシート(構造)の比較、2nm世代のセミダマシン配線におけるエアギャップ絶縁と低誘電率(Low K)絶縁の比較、2nm世代のセミダマシン配線と3nm世代のデュアルダマシン配線の比較、である。数値の赤字は、基準値である配置配線(PnR)後のシミュレーション結果とのズレが動作周波数で1.05以上、消費電力で1.10以上に達した場合(差異が大きい場合)[クリックで拡大] 出所:imec(2021年4月に開催された国際学会「2021 Electron Device Technology and Manufacturing Conference(EDTM)でimecが発表した論文「Disruptive Technology Elements, and Rapid and Accurate Block-Level Performance Evaluation for 3nm and Beyond」から)Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増