EE Times Japan >

LSI >

「システム・製造協調最適化(STCO)」の実現技術(後編):福田昭のデバイス通信(327) imecが語る3nm以降のCMOS技術(30)(2/2 ページ)

» 2021年10月11日 11時30分 公開

[福田昭,EE Times Japan]

チップレットの普及でSTCOの要求が強まる

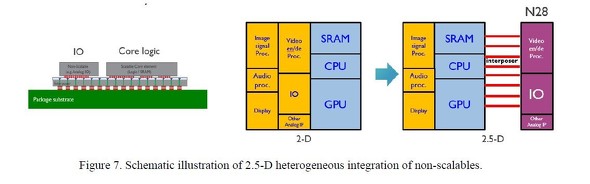

このほか、チップレット(2.5次元/3次元の集積化)もSTCOであらかじめ性能を見積もることが望ましい。7nm世代以降は、チップレット化が加速するとみられる。従来の大規模CMOSロジックでは、シリコン全体を微細化によって縮小することが性能向上とコスト削減を両立させていた。しかし7nm世代以降は、システムLSIあるいはSoC(System on a Chip)を構成する回路ブロック(あるいはマクロ)の中で、微細化が困難な部分の割合が増加する。ミックスドシグナル回路や入出力回路、アナログ回路などだ。

こうなると7nm技術で1枚のシリコンダイに全ての回路を作り込むよりも、微細化が困難な回路ブロックは従来技術(14nm技術あるいはそれ以前の技術)による別のシリコンダイに分割して2.5次元/3次元集積することが、「消費電力と性能、シリコン面積、コスト(PPAC)」のバランスで優れていることが少なくない。

チップレット化と2.5次元集積の概念。微細化が難しいビデオコーデック、入出力、アナログの回路ブロックは別のシリコンに分割し、安価な28nm世代(N28)のプロセス技術で製造する[クリックで拡大] 出所:imec(2018年2月に開催された国際学会「SPIE Advanced Lithography」でimecが発表した論文「imec N7, N5 and beyond: DTCO, STCO and EUV insertion strategy to maintain affordable scaling trend」から)

チップレット化と2.5次元集積の概念。微細化が難しいビデオコーデック、入出力、アナログの回路ブロックは別のシリコンに分割し、安価な28nm世代(N28)のプロセス技術で製造する[クリックで拡大] 出所:imec(2018年2月に開催された国際学会「SPIE Advanced Lithography」でimecが発表した論文「imec N7, N5 and beyond: DTCO, STCO and EUV insertion strategy to maintain affordable scaling trend」から)システムを複数のシリコンダイで構成したとしても、あらかじめシステムの速度や消費電力、コストなどを見積もっておくことが望ましい。2.5次元/3次元の集積化技術に適応したSTCOの要求が強まっていく。

(次の記事を読む)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

ルネサス、供給確保で21年7〜9月期売上高2400億円目指す

ルネサス、供給確保で21年7〜9月期売上高2400億円目指す

ルネサス エレクトロニクスは2021年7月29日、2021年12月期第2四半期(4〜6月)業績(Non-GAAPベース)を発表した。第2四半期3カ月間の売上高は2179億円で前年同期比30.7%増、営業利益は614億円で同2.03倍と大幅な増収増益になった。売上総利益率は52.0%、営業利益率は28.2%だった。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説する。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

今回は「強誘電体メモリ(FeRAM)」を取り上げる。FeRAMの記憶原理と、60年以上に及ぶ開発の歴史を紹介しよう。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR