「システム・製造協調最適化(STCO)」の実現技術(前編):福田昭のデバイス通信(326) imecが語る3nm以降のCMOS技術(29)

7nm以降の技術ノードでは、「設計・製造協調最適化(DTCO)」だけでなく、「システム・製造協調最適化(STCO:System Technology Co-Optimization)」も利用することでPPAあるいはPPACのバランスを調整することが求められるようになってきた。

設計・製造協調最適化(DTCO)とその限界

半導体のデバイス技術とプロセス技術に関する世界最大の国際学会「IEDM(International Electron Devices Meeting)」は、「チュートリアル(Tutorials)」と呼ぶ技術講座を本会議(技術講演会)とは別に、プレイベントとして開催してきた。2020年12月に開催されたIEDM(Covid-19の世界的な流行によってバーチャルイベントとして開催)、通称「IEDM2020」では、合計で6本のチュートリアル講演が実施された。その中で「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」が非常に興味深かった。講演者は研究開発機関のimecでTechnology Solutions and Enablement担当バイスプレジデントをつとめるMyung‐Hee Na氏である。

そこで本講座の概要を本コラムの第298回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

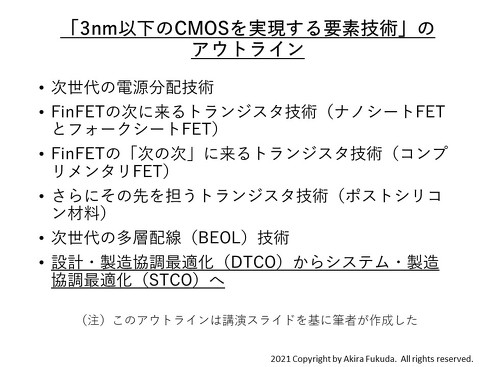

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。前回から、「設計・製造協調最適化(DTCO)からシステム・製造協調最適化(STCO)へ」の講演パートを紹介している[クリックで拡大]

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。前回から、「設計・製造協調最適化(DTCO)からシステム・製造協調最適化(STCO)へ」の講演パートを紹介している[クリックで拡大]本シリーズの前回(第28回)から、6番目(最後)のパートである「設計・製造協調最適化(DTCO)からシステム・製造協調最適化(STCO)へ」の講演概要を紹介している。前回ではデバイスの3次元化により、22nm/16nm世代からは「設計・製造協調最適化(DTCO:Design Technology Co-Optimization)」技術が導入されるようになったことを述べた。FinFETの採用によって加工寸法の微細化だけでなく、基本セル(スタンダードセル)を縮小する要素技術によってトランジスタ密度を従来と同様の比率で高める。このとき、設計ルールとプロセス条件の両方から、「消費電力と性能、シリコン面積(PPA:Power、Performance、Area)」を要求仕様に準じてレイアウト設計の段階で最適化する手法としてDTCOを駆使するようになった。

しかし7nm以降の技術ノードでは、DTCOだけでは最適化が難しくなりつつある。その理由は主に2つ。1つは要素技術の増加と複雑化、もう1つはチップレット化(2.5次元/3次元の集積化)である。基本セル(スタンダードセル)のレイアウト設計を最適化するDTCOに加え、大規模な回路ブロックやサブシステムなどでの最適化手法「システム・製造協調最適化(STCO:System Technology Co-Optimization)」を利用することによってPPAあるいはPPAC(CはCost)のバランスを調整することが求められるようになってきた。

要素技術が複雑に絡む状態で回路ブロックの電力と速度を見積もる

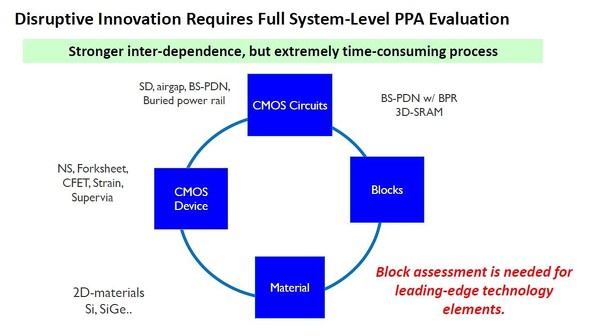

前回でも述べたように、CMOSロジックを構成する階層(トランジスタ材料、トランジスタ技術、相互接続技術、回路ブロック/サブシステム)の全てで、新たな要素技術が今後は使われていく可能性が高い。これらの要素技術はお互いに影響し合う。

3nm以降のCMOSロジックを構成する階層と新たな要素技術群。新たな要素技術群は製造に時間がかかるとともに、相互に影響し合う[クリックで拡大] 出所:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料)

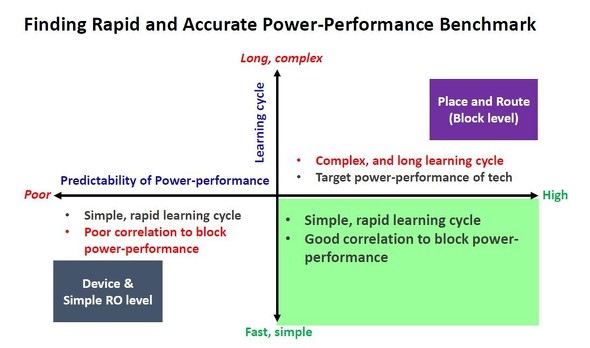

3nm以降のCMOSロジックを構成する階層と新たな要素技術群。新たな要素技術群は製造に時間がかかるとともに、相互に影響し合う[クリックで拡大] 出所:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料)要素技術が複雑に絡み合う状態で、CMOSロジックの消費電力(Power)と性能(Performance)を素早くかつ正確に見積もりたい。最も精度が高いのは、マスクレイアウト設計において回路ブロックの配置配線(PnR:Placement and Routing)を完了してから、消費電力と性能を推定することだろう。ただし配置配線を完了させるには相当な時間を要する。そして最適な条件を出すためには通常、配置配線を何回か繰り返すことが求められる。

最も素早く見積もれるのは、小規模なモニター回路の利用だろう。標準なモニター回路は、リング発振器(RO:Ring Oscillator)である。ROは奇数段のインバータ論理による閉回路(ループ状の回路)で構成されており、シミュレーションによって短時間で消費電力(動作時および待機時)と動作周波数(伝搬遅延時間)を見積もれる。ただし、回路ブロック全体の消費電力と動作周波数を推定したときの精度は高くない。

CMOS回路ブロックの消費電力(Power)と性能(Performance)を見積もる手法と利害得失。右上は配置配線による見積もり。高精度だが時間がかかる。左下はリング発振器(RO)による見積もり。迅速だが精度は低い。右下に相当する「短時間かつ高精度」の推定手法が望まれる[クリックで拡大] 出所:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料)

CMOS回路ブロックの消費電力(Power)と性能(Performance)を見積もる手法と利害得失。右上は配置配線による見積もり。高精度だが時間がかかる。左下はリング発振器(RO)による見積もり。迅速だが精度は低い。右下に相当する「短時間かつ高精度」の推定手法が望まれる[クリックで拡大] 出所:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料)このため、短時間かつ高精度で回路ブロックの消費電力と性能(動作周波数)を推定可能な手法が望まれる。

(後編に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

ルネサス、供給確保で21年7〜9月期売上高2400億円目指す

ルネサス、供給確保で21年7〜9月期売上高2400億円目指す

ルネサス エレクトロニクスは2021年7月29日、2021年12月期第2四半期(4〜6月)業績(Non-GAAPベース)を発表した。第2四半期3カ月間の売上高は2179億円で前年同期比30.7%増、営業利益は614億円で同2.03倍と大幅な増収増益になった。売上総利益率は52.0%、営業利益率は28.2%だった。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説する。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

今回は「強誘電体メモリ(FeRAM)」を取り上げる。FeRAMの記憶原理と、60年以上に及ぶ開発の歴史を紹介しよう。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増