システムの性能向上に不可欠となった先進パッケージング技術:福田昭のデバイス通信(329) TSMCが開発してきた最先端パッケージング技術(2)(1/2 ページ)

今回は、フロントエンド3Dとバックエンド3Dを解説する他、TSMCが「CSYS(Complementary Systems, SoCs and Chiplets integration、シーシス)」と呼ぶソリューションを紹介する。

独自開発の先進パッケージ技術を「3D Fabric」と呼称

高性能プロセッサとその関連技術に関する国際学会「Hot Chips」がことし(2021年)8月22日〜24日にオンラインで開催された。「Hot Chips」は高性能プロセッサの最新技術情報を入手できる貴重な機会として知られている。会期は3日間で、初日が「チュートリアル(Tutorials)」と呼ぶ技術講座、2日目と3日目が「カンファレンス(Conference)」と呼ぶ技術講演会となっており、講演会とは別にポスター発表の機会も用意される。オンライン開催となったことしは、あらかじめ録画されたビデオをプログラムに沿って公開する形式となった。参加登録者は開催後も一定の期間は、オンデマンドで講演を聴講できる。

初日の「チュートリアル(Tutorials)」では、13件の講演が実施された。その中で「先進パッケージング技術」に関する講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」が極めて興味深かった。講演者はTSMCで研究開発担当バイスプレジデント(現在はシステム集積化手法開発担当バイスプレジデント)をつとめるDouglas Yu氏である。

そこで本講演の概要を前回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

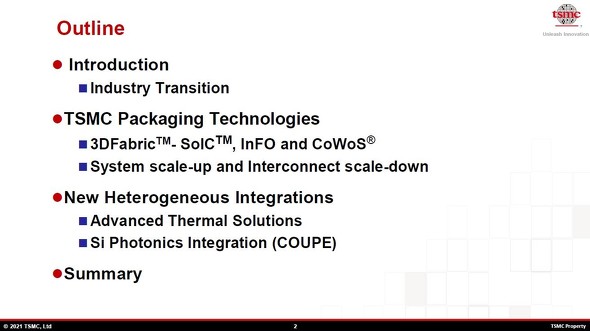

講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」のアウトライン[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」のアウトライン[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)前回は、講演のアウトラインを説明するとともに、TSMCが「3D Fabric」と呼ぶ2.5/3次元(2.5/3D)の集積化技術の概要を簡単に説明した。「3D Fabric」は2020年8月にTSMCが呼称し始めたブランド名で、過去に同社が開発してきた複数の先進パッケージング技術を総称するものだ。

技術世代やプロセス技術などが異なる複数のダイを組み合わせる

前回でも述べたように、「3D Fabric」はフロントエンド3D(FE 3D)とバックエンド3D(BE 3D)の2つの技術で構成される。フロントエンド3D(FE 3D)には、「SoIC(System on Integrated Chips)」と呼ぶシリコンダイの積層接続技術がある。シングルダイのシステムLSI(SoC:System on a Chip)を意図的に複数のダイ(チップレット)に分割する「チップレット化」を支える技術だ。最近になって量産が始まった。

バックエンド3D(BE 3D)には、複数のシリコンダイを高密度に相互接続する2つの技術がある。1つはモバイル向けに開発した「InFO(Integrated Fan-Out、インフォ)」、もう1つは高性能コンピューティング(HPC)向けに開発した「CoWoS(Chip on Wafer on Substrate、コワース)」だ。いずれも豊富な量産実績を有する。

「3D Fabric」を構成するフロントエンド3D(左側)とバックエンド3D(右側)[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

「3D Fabric」を構成するフロントエンド3D(左側)とバックエンド3D(右側)[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)フロントエンド3DのSoICには、大別すると2つの構成がある。1つは製造技術世代の異なる複数の小さなシリコンダイ(ミニダイ)で1つのシステム(従来のシステムLSIに相当)を実現する構成(チップレット構成)だ。最先端であるN世代で製造したミニダイや1つ前の世代であるN-1世代、さらに前の世代であるN-2世代で製造したミニダイなどを組み合わせる。

もう1つは、プロセス技術の異なる複数のシリコンダイで1つのモジュールを実現する構成(ヘテロジニアス構成)である。例えばロジックのプロセス技術で製造したシリコンダイと、メモリのプロセス技術で製造したシリコンダイを組み合わせる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増