システムの性能向上に不可欠となった先進パッケージング技術:福田昭のデバイス通信(329) TSMCが開発してきた最先端パッケージング技術(2)(2/2 ページ)

最先端の半導体は「CMOS」から「CSYS」へ

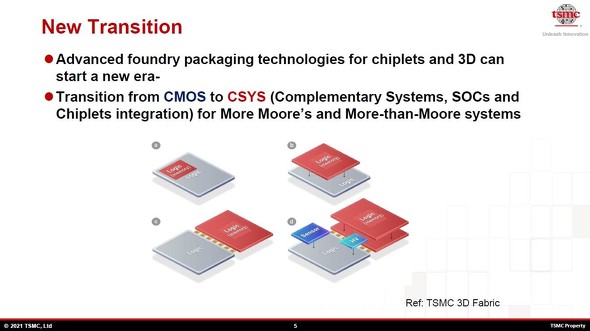

過去には半導体開発は技術世代を1つ進めるごとに、1つのシリコンダイ(シングルチップあるいはシングルダイ)に搭載するトランジスタの数をおおよそ2倍に増やしてきた。逆に見ると、同じトランジスタ数の集積に必要なシリコン面積を技術世代ごとおよそ半分に減らしてきた。前提となっていたのは、可能な限り多くの回路をCMOSのシングルダイに詰め込む「モノリシック集積の最大化」という考え方だ。

しかし現在、7nmや5nmといった最先端のCMOS製造技術世代では、技術世代やプロセス技術の異なる複数のダイによる組み合わせでシステムを構成することが最適なソリューションとなりつつある。TSMCはこのソリューションを「CSYS(Complementary Systems, SoCs and Chiplets integration、シーシス)」と呼ぶ。

「CMOS」から「CSYS(Complementary Systems, SoCs and Chiplets integration)」へ。チップレットと3次元集積技術によってムーアの法則を延命する(More Moore)、あるいはムーアの法則を超える(More-than-Moore)[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

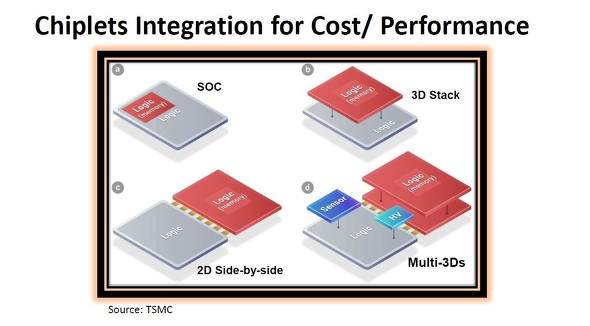

「CMOS」から「CSYS(Complementary Systems, SoCs and Chiplets integration)」へ。チップレットと3次元集積技術によってムーアの法則を延命する(More Moore)、あるいはムーアの法則を超える(More-than-Moore)[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから) システムを構成する半導体技術の例。(a)は従来のシステムLSI(SoC)。シングルダイで最大規模の回路を実現する。(b)はロジックダイにロジックダイ(あるいはメモリダイ)を積層するSoICの例。(c)はロジックダイとロジックダイ(あるいはメモリダイ)を水平方向に並べた構成。(d)は、(c)をベースにセンサーのダイや高電圧回路(HV)のダイ、ロジックダイ(あるいはメモリダイ)を積層するSoICの例[クリックで拡大] 出所:TSMC(2020年12月に開催された国際学会IEDMのショートコース「Advanced 3D System Integration Technologies」のスライドから)

システムを構成する半導体技術の例。(a)は従来のシステムLSI(SoC)。シングルダイで最大規模の回路を実現する。(b)はロジックダイにロジックダイ(あるいはメモリダイ)を積層するSoICの例。(c)はロジックダイとロジックダイ(あるいはメモリダイ)を水平方向に並べた構成。(d)は、(c)をベースにセンサーのダイや高電圧回路(HV)のダイ、ロジックダイ(あるいはメモリダイ)を積層するSoICの例[クリックで拡大] 出所:TSMC(2020年12月に開催された国際学会IEDMのショートコース「Advanced 3D System Integration Technologies」のスライドから)従来、異なるプロセス技術によるシリコンダイは1つにせず、プロセス技術ごとにシリコンダイを製造して1つのパッケージにまとめた方が全体としてはコストが低くなるとされていた。しかし7nmや5nmといった最先端ノードでは、ロジックプロセスの微細化によるコストが上昇するとともに、微細化が適用困難な回路ブロックの割合が増大してきた。

そこで微細化のメリットが大きな回路ブロックだけに、最先端のプロセスを適用することがごく普通になりつつある。相対的に、複数のダイを2.5/3次元に接続して集積化する技術、すなわち先進パッケージング技術の比重が高まる。より厳密には、最先端システムの開発には先進パッケージング技術が不可欠となりつつある、と言えよう。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

「システム・製造協調最適化(STCO)」の実現技術(前編)

「システム・製造協調最適化(STCO)」の実現技術(前編)

7nm以降の技術ノードでは、「設計・製造協調最適化(DTCO)」だけでなく、「システム・製造協調最適化(STCO:System Technology Co-Optimization)」も利用することでPPAあるいはPPACのバランスを調整することが求められるようになってきた。 「システム・製造協調最適化(STCO)」の実現技術(後編)

「システム・製造協調最適化(STCO)」の実現技術(後編)

本シリーズの最終回となる今回は、前回に続き「システム・製造協調最適化(STCO)」を解説する。 欧州が欧州半導体法「European Chips Act」の策定へ

欧州が欧州半導体法「European Chips Act」の策定へ

欧州委員会委員長であるUrsula von der Leyen氏が2021年9月15日(現地時間)、一般教書演説の中で、「European Chips Act(欧州半導体法)」の策定に関する発表を行った。中国政府が半導体イノベーションに数十億米ドル規模の資金を投じていることや、米国議会が半導体の戦略的価値について合意に達したことなどを受け、EUは、主体的な最先端技術の実現を目指す法案を策定し、競争に参入していく考えを表明した。 第4世代R-Car SoCも発表、ルネサスが語る車載戦略

第4世代R-Car SoCも発表、ルネサスが語る車載戦略

ルネサス エレクトロニクスは2021年10月6日、オンラインで記者説明会を実施。同社オートモーティブソリューション事業本部の事業本部長、片岡健氏が車載事業戦略について語った。 埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説する。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増