混載MRAMの書き換えエネルギーを72%削減、ルネサス:IoT用マイコンの低電力化に向け(2/2 ページ)

時間経過とともに印加電圧を増加

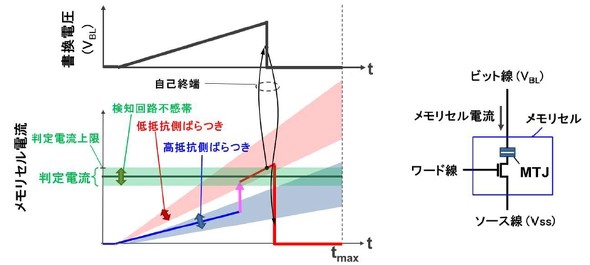

従来は、高抵抗状態から低抵抗状態への書き換え時に、一定の電圧を印加していたのに対し、スロープパルス方式では、時間経過とともに印加電圧を高くしていく。メモリセルの特性ばらつきなどによってメモリセル電流が検知回路の検知レベルに到達しなかった場合でも、書き換え電圧が少しずつ高くなるので、メモリセル電流も増加し、最終的に検知レベルを超えるので、書き換え完了を検知し、書き換え電圧の印加を終了することができる。これにより、書き換え完了を安定して検知できるようになる。

なお、低抵抗状態から高抵抗状態への書き換え時は、メモリセル電流が大電流から小電流に遷移するので、スロープ電圧では完了を検知できないが、その際は、電流源回路で書き換え電流をスロープで増加させ、メモリセル電圧で判定する。

10%のビット書き損じを許容

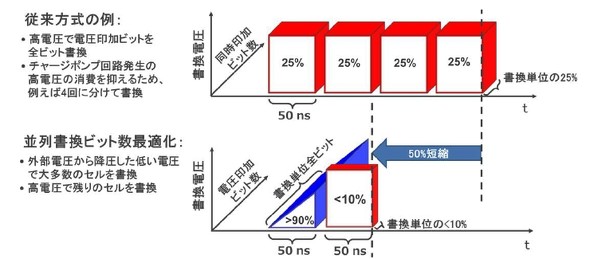

同時書き換えビット数の最適化技術は、ビットの書き損じを許容することで、書き換え電圧を大幅に下げ、結果的に書き換え電圧印加時間を短縮するというもの。

一般的に、MRAMの書き換え電圧は全ビットが十分書き換えられる条件で決定する。これには高い書き換え電圧が必要となるので、チャージポンプ回路を用いる。チャージポンプ回路の追加によるチップ面積や消費電力の増加をなるべく抑えるために、MRAMマクロの書き換え単位を分割する。例えば128ビットを一気に書き換えるのではなく、4分割して32ビットずつ4回書き換える、といったイメージだ。だがその分、書き換え電圧の印加時間は4倍長くなる。

ルネサスが開発した同時書き換えビット数の最適化技術では、全体の10%の書き損じを1回目の印加で許容する。128ビットのMRAMマクロを例にとると、マイコンの外部電圧(IO用電源)から降圧した電圧で、128ビット全てに一括印加して90%以上を書き換える。その後、書き換えが完了しなかった10%以下のビットのみ、チャージポンプ回路で生成した高い書き換え電圧で書き換える。これにより、書き換え電圧の印加が2回で済み、4分割以上していた場合に比べて書き換え電圧の印加時間を50%以上短縮できる。「チャージポンプ回路の大きさも、4分割する場合に比べて、40%程度で済む」(ルネサス)

さらに、1回目の書き換えに、スロープパルス方式を用いた自己終端書き換えも適用するので、書き換えエネルギーも削減できる。

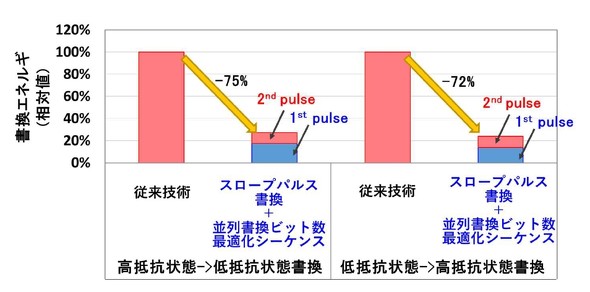

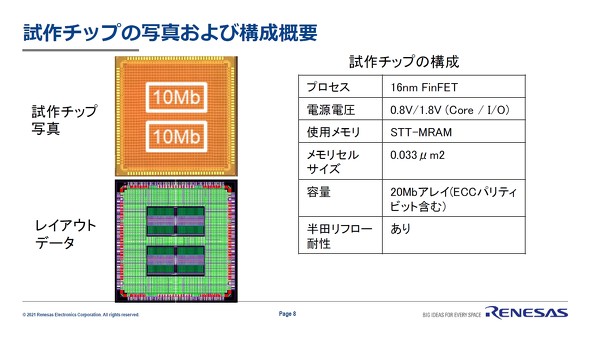

これら2つの回路技術を適用したテストチップでは、72%の書き換えエネルギーの低減と、50%の書き換え電圧印加時間の低減を確認した。なお、このテストチップは、16nm FinFETプロセスへの混載MRAM技術で試作した20MビットのMRAMメモリセルアレイを搭載したものとなる。

ルネサスは「当社は1Xnm移行の世代では、ファウンドリーの新興メモリ(MRAM、磁気抵抗メモリ)を活用することも選択肢の一つとして考えており、数年先の適用を想定して、設計的な付加価値を創出する研究開発を進めている」と語り、その成果の一つが今回の発表だとした。

関連記事

MRAMのメモリセルと読み書きの原理

MRAMのメモリセルと読み書きの原理

今回は、MRAMのメモリセルの構造と、データの読み出しと書き込みの原理をご説明する。 東京工大ら、SOT-MRAM素子の原理動作実証に成功

東京工大ら、SOT-MRAM素子の原理動作実証に成功

東京工業大学と米国カリフォルニア大学ロサンゼルス校を中心とした国際研究チームは、トポロジカル絶縁体と磁気トンネル接合(MTJ)を集積したスピン軌道トルク磁気抵抗メモリ(SOT-MRAM)素子を試作し、読み出しと書き込みの原理動作を実証した。 次世代メモリ市場、2031年までに440億米ドル規模へ

次世代メモリ市場、2031年までに440億米ドル規模へ

米国の半導体市場調査会社であるObjective AnalysisとCoughlin Associatesは、共同執筆した年次レポートの中で「次世代メモリが、さらなる急成長を遂げようとしている」という見解を示した。次世代メモリ市場は2031年までに、440億米ドル規模に達する見込みだという。 産総研、MRAMの磁気安定性を飛躍的に改善

産総研、MRAMの磁気安定性を飛躍的に改善

産業技術総合研究所(産総研)は、原子層レベルで制御されたタンタル(Ta)を下地に用いることで、磁気抵抗メモリ(MRAM)の磁気安定性を飛躍的に改善する技術を開発した。 2021年に最も売上高成長を果たす半導体メーカーはAMDか

2021年に最も売上高成長を果たす半導体メーカーはAMDか

IC Insightsは2021年11月、半導体メーカー売上高上位25社の2021年売上高成長率予測を発表した。それによると、2021年に最も2020年比で売上高を伸ばす半導体メーカーは、AMDだという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増