東京工大ら、SOT-MRAM素子の原理動作実証に成功:トポロジカル絶縁体とMJTを集積

東京工業大学と米国カリフォルニア大学ロサンゼルス校を中心とした国際研究チームは、トポロジカル絶縁体と磁気トンネル接合(MTJ)を集積したスピン軌道トルク磁気抵抗メモリ(SOT-MRAM)素子を試作し、読み出しと書き込みの原理動作を実証した。

超低消費電力SOT-MRAMの開発を加速

東京工業大学工学院電気電子系のファム・ナムハイ准教授と米国カリフォルニア大学ロサンゼルス校のカン・ワン教授を中心とした国際研究チームは2021年10月、トポロジカル絶縁体と磁気トンネル接合(MTJ)を集積したスピン軌道トルク磁気抵抗メモリ(SOT-MRAM)素子を試作し、読み出しと書き込みの原理動作を実証したと発表した。

MRAMは、不揮発で高速動作、耐久性に優れるなど、さまざまな特長を備えたメモリである。現行の製品は書き込み技術として、「スピン・トランスファー・トルク(STT)法」を用いているが、この方法だとデータを書き込む時のエネルギーが従来の揮発性メモリに比べ1桁大きい、などの課題があった。

ファム准教授らは、スピン軌道トルク(SOT)を用いた磁化反転の技術に着目した。SOT-MRAMは、スピンホール効果のスピンホール角(θSH)が「1」以上で、高い電気伝導性を持つスピンホール材料を開発することができれば、メモリ素子の磁化反転に必要な電流を1桁、エネルギーを2桁以上も下げることができるという。

そこで、スピンホール材料としてθSHが小さい重金属(タンタルやプラチナ、タングステンなど)に代わり、スピンホール角の大きいトポロジカル絶縁体が検討されてきた。しかし、MRAMでトポロジカル絶縁体と磁気トンネル接合を集積するための技術は、これまで確立されていなかったという。

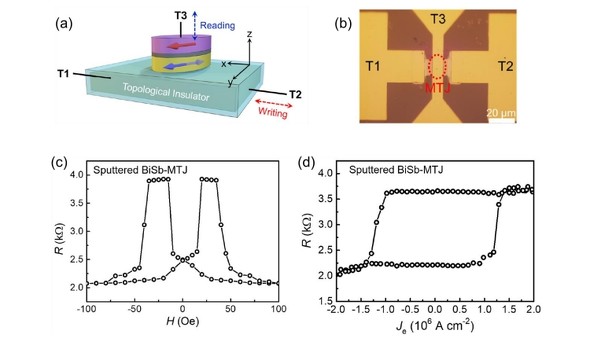

共同研究チームは今回、3端子のSOT-MRAM素子を作製するため、以下の製造プロセスを用いた。まず、下部電極には、分子線エピタキシャル結晶成長法により製膜をした(Bi、Sb)2Te3トポロジカル絶縁体または、スパッタリング法により製膜をしたBiSbトポロジカル絶縁体を配置した。そして、中間層にトポロジカル絶縁体と似た結晶構造を持つRu(5nm)を、その上にCoFeB(2.5nm)/MgO(2nm)/CoFeB(5nm)のMTJを製膜。その後に、250〜300℃の温度で熱処理を行い、磁性層のCoFeBを結晶化させた。

試作したSOT-MRAM素子はサイズが4×8μm2〜100×200nm2と小さい。スパッタリング法のみで作製したBiSbトポロジカル絶縁体‐磁気トンネル接合のSOT-MRAM素子(1×3μm2)を用いて、トンネル磁気抵抗効果を測定した。この素子は250℃で熱処理を行ったが、90%という比較的高い抵抗変化を達成。また、スピン軌道トルクによる低電流密度の書き込みにも成功した。

上図は3端子SOT-MRAM素子の模型と素子の写真、下図はスパッタリング法のみで作製したBiSb-MTJ素子のトンネル磁気抵抗効果と、スピン軌道トルクによる書き込みの実証[クリックで拡大] 出所:東京工業大学他

上図は3端子SOT-MRAM素子の模型と素子の写真、下図はスパッタリング法のみで作製したBiSb-MTJ素子のトンネル磁気抵抗効果と、スピン軌道トルクによる書き込みの実証[クリックで拡大] 出所:東京工業大学他今回の研究成果により、トポロジカル絶縁体と磁気トンネル接合を集積した素子を作製し、読み出しと書き込みの原理動作を初めて確認することができたという。

関連記事

レドックス・フロー熱電発電で発電密度を1桁向上

レドックス・フロー熱電発電で発電密度を1桁向上

東京工業大学の研究グループは、排熱源を冷却しながら発電を行う「レドックス・フロー熱電発電」で、従来に比べ発電密度を1桁以上高くすることに成功した。 スマホでAI処理を行うプロセッサアーキテクチャ

スマホでAI処理を行うプロセッサアーキテクチャ

東京工業大学は、高度なAI処理をスマートフォンなどで実行できる「プロセッサアーキテクチャ」を開発した。試作したチップの実効効率は最大26.5TOPS/Wで、世界トップレベルだという。 日本大学ら、磁性物質の量子性を圧力によって制御

日本大学ら、磁性物質の量子性を圧力によって制御

日本大学などの研究グループは、1万気圧以上の高圧力中において、鎖状の磁性体である三塩化セシウム銅の磁気測定と理論モデルによる解析を行い、圧力によって量子性の強さが制御できることを実証した。 量子センサーのスピン情報、電気的読み出しに成功

量子センサーのスピン情報、電気的読み出しに成功

東京工業大学と産業技術総合研究所(産総研)の共同研究グループは、ダイヤモンド量子センサーのスピン情報を、電気的に読み出すことに成功した。感度が高い集積固体量子センサーの実現が期待される。 ギャップ長20nmのナノギャップガスセンサーを開発

ギャップ長20nmのナノギャップガスセンサーを開発

東京工業大学は、抵抗変化型ガスセンサーの電極間隔(ギャップ長)を20nmと狭くしたナノギャップガスセンサーを開発した。ギャップ長が12μmの一般的な酸素ガスセンサーに比べ、約300倍の応答速度を実現した。 東京工大、電源不要のミリ波帯5G無線機を開発

東京工大、電源不要のミリ波帯5G無線機を開発

東京工業大学は、無線電力伝送で生成される電力で動作させることができる、「ミリ波帯5G中継無線機」を開発した。電源が不要となるため基地局の設置も容易となり、ミリ波帯5Gのサービスエリア拡大につながるとみられている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- 次世代パワー半導体 「期待の5材料」の現在地

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- パワー停滞も光デバイス堅調、三菱電機の半導体部門

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 「3社のパワー半導体事業を切り出し合弁設立したい」三菱電機社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼