AMDの最新GPU「Radeon RX 6500 XT」戦略を読み解く:この10年で起こったこと、次の10年で起こること(62)(2/4 ページ)

ミドルやエントリークラスでも先端プロセスへの移行が進む

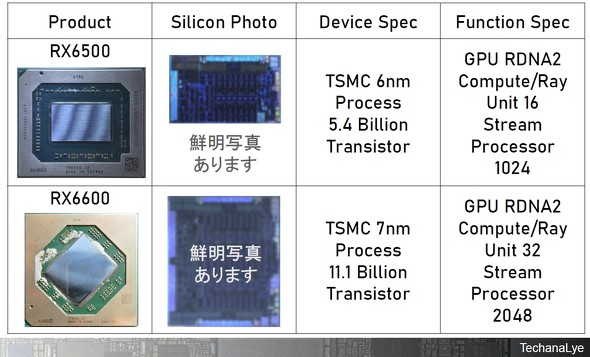

表1は、上段が2022年1月発売のRadeon RX 6500 XT、下段が2021年10月発売のRadeon RX 6600である。おのおののシリコンに搭載されるコア数は2倍の差があり、またメモリインタフェース数などもほぼ2倍の差となっている。一番大きな違いは、Radeon RX 6600が7nmプロセスで製造されるのに対して、Radeon RX 6500 XTは6nmとより微細な製造プロセスを用いていることにある。弊社が間もなく入手するIntelのGPU「Arc Aシリーズ」も6nmなので、Radeon RX 6500 XTとの比較を行う予定である。

2021年から2022年にかけてプロセッサ(モバイルもHPCも)ではミドルとエントリーが6nm、ハイエンドが4nmに移行しており、AMDはエントリーモデルに真っ先に6nmを用いたわけである。今後ハイエンドは新アーキテクチャに移行していくので、2022年後半から2023年、2024年にかけてCPUでは「Zen 4」、GPUでは「RDNA 3」などがリリースされ、5nmや4nmが活用されていく。

RX 6600の上半分を“切り出した”RX 6500

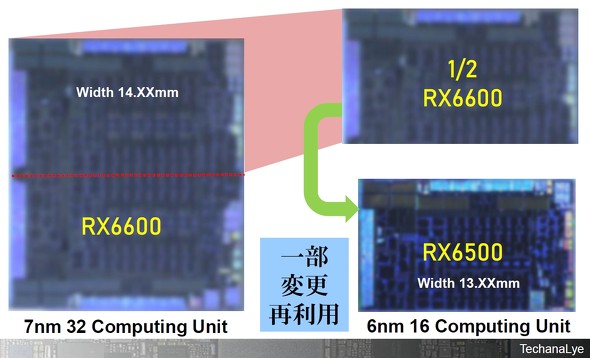

図2は、7nmプロセスで製造されるミドル向けのRadeon RX 6600と、6nmプロセスで製造されるRadeon RX 6500 XTの関係である。表1の仕様の通り、Radeon RX 6500 XTは、Radeon RX 6600をほぼ完全にカットダウンした構造になっている。シリコンの上半分を切り出して、一部インタフェースを置き換えているだけだ。

AppleのM1 Ultraが「M1 Max」を2個並べて、インターポーザーで接続しているのに対して、AMDではミドルのシリコン(実際には設計データ)を半分にカットし、エントリーを作り出している。設計データをそのまま活用するので、カットそのものは秒で終わるだろう。その後、データの検証を行い、マスクを作り、製造してRadeon RX 6500 XTは生まれたわけだ。

6nmは7nmの派生プロセスである。半導体プロセスはフルノードとハーフノードを繰り返している。フルノード(新規プロセス)の開発には膨大な手間と費用がかかるが、フルノードの歩留まりや特性が安定してくると、サイズを数パーセントから10%ほどシュリンクしたハーフノードを作り*)、シリコン面積を小さくすることでウエハーからのチップ取得数を増やし、コストダウンを図る。エントリー向けGPUであるRadeon RX 6500 XTはさらにコストダウンを行えるように、6nmプロセスを用い、図2のようにシリコンサイズを7nmプロセスよりも小さくしているのだ。

*)ゲートだけをシュリンクする場合も多い。例としては、MediaTekの「Dimensity 1000」(7nm)→「Dimensity 1200(6nm)」がある。これら2つのチップはシリコン面積が同じ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す

- ルネサス26年1Qは増収増益 車載/AI好調で「足元は当面強い」