「IMW2022」3D NANDの最前線 〜EUV適用から、液体窒素冷却の7ビット/セルまで:湯之上隆のナノフォーカス(51)(3/5 ページ)

多層化のトップを快走するMicronの3D NAND

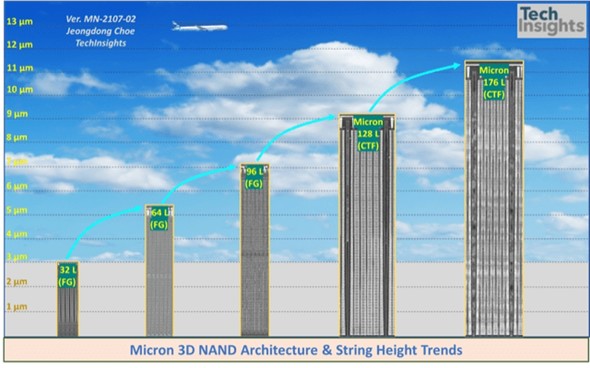

2次元の微細化を続けてきたNANDは、2016年頃に3次元化した。その後、メモリ密度を上げるために、各社はひたすら3次元の積層数を増大させている。例えば、Micronは、32層、64層、96層、128層、そしてどこよりも早く176層の生産を開始した(図9)。

図9 高層化が進む3D NANDの積層数(Stack Height -Scaling) 出所:JEONGDONG CHOE , “Micron B47R 3D CTF CuA NAND Die, World’s First 176L (195T)”, AUGUST 19TH, 2021 , https://semiengineering.com/micron-b47r-3d-ctf-cua-nand-die-worlds-first-176l-195t/

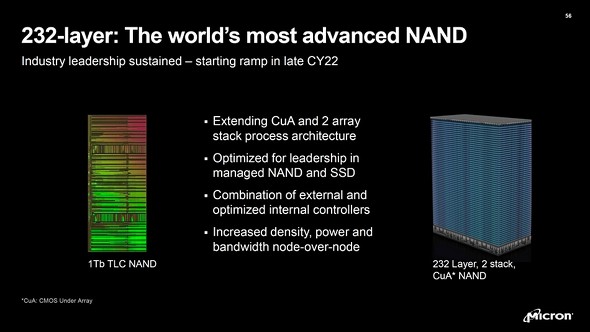

図9 高層化が進む3D NANDの積層数(Stack Height -Scaling) 出所:JEONGDONG CHOE , “Micron B47R 3D CTF CuA NAND Die, World’s First 176L (195T)”, AUGUST 19TH, 2021 , https://semiengineering.com/micron-b47r-3d-ctf-cua-nand-die-worlds-first-176l-195t/さらに、IMW2022が開催される直前の2022年5月13日に、Micronが2022年の後半から232層の3D NANDを生産することが報じられた(図10)。この232層の3D NANDは、116層の2段積みになっている。そして、メモリセルアレイの下部にCMOS回路を形成する、いわゆるCMOS Under Array(CUA)の構造を採用している。

図10 Micronが232層の3D NANDを発表 出所:Chris Mellor, “Micron reveals flash roadmap to 500+ layer 3D NAND”, May 13, 2022, https://blocksandfiles.com/2022/05/13/micron-flash-roadmap/

図10 Micronが232層の3D NANDを発表 出所:Chris Mellor, “Micron reveals flash roadmap to 500+ layer 3D NAND”, May 13, 2022, https://blocksandfiles.com/2022/05/13/micron-flash-roadmap/MicronのIMW2022の発表

3D NANDのメモリ密度を増大させるために積層数を増やす方法は単純ではあるが、アスペクト比(Aspect Ratio、AR)の高いメモリホールの開口や、その埋め込みなど、課題は山積している。

そこで、Micronは、積層数の増大に頼るだけでなく、メモリセルを平面方向、つまりX-Y方向にスケーリングすることにより、メモリ密度を増大することを提案している。

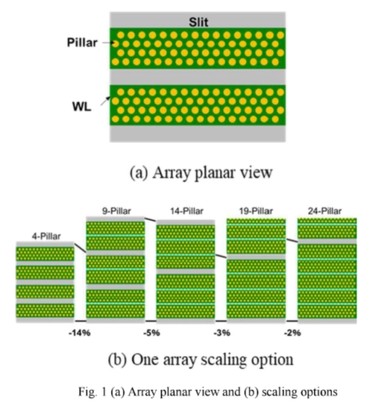

図11(a)は、メモリセルアレイの平面図である。ピラーと呼ばれる小さな円がアレイスタックを上下に貫通している。ピラーを囲んでいるワードライン(WL)は、ストレージデバイスのゲートとして機能する。つまり、ピラーとWLの交点がストレージデバイスのメモリセルを形成している。このセルが、異なるレベルの閾値電圧(Vt)で、データを2進法で記憶する。

図11 Stack Heighを抑えるためのX-Y Scaling 出所:Lars Heineck and Jin Liu(Micron), “3D NAND Flash Status and Trends”, IMW2022, Proceedings, Fig.1

図11 Stack Heighを抑えるためのX-Y Scaling 出所:Lars Heineck and Jin Liu(Micron), “3D NAND Flash Status and Trends”, IMW2022, Proceedings, Fig.1WL間のギャップはスリットと呼ばれており、メモリセルアレイの形成に必要な構造となっている。3D NANDでは、犠牲WL材料の除去とメタルゲートの形成がスリットを介して行われるからだ。

このような構造のメモリセルについて、X-Yスケーリングには二つの方法がある。一つはスリット幅を縮小すること、もう一つはピラーを密に配置することである。この手法を、ピラーピッチスケーリングと呼ぶ。

図11(b)は、スリット間のピラー数を、4ピラー、9ピラー、14ピラー、24ピラーと高密度化した場合のメモリセルの平面図を示している。スリット間のピラー数が14を超えると、スケーリングのメリットが減少し始める。従って、やみくもにピラーピッチスケーリングを行えばよいというわけではないことが分かる。

3D NANDの2つのスケーリング

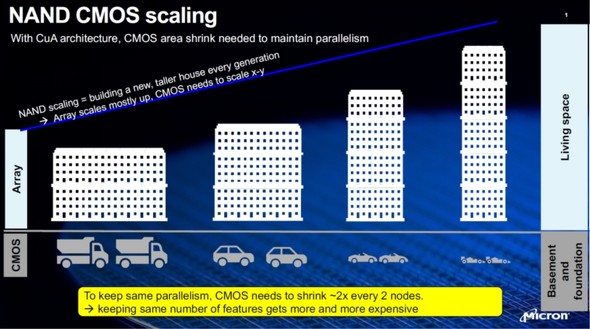

3D NANDのメモリ密度を増大するには、2つの方法があるわけだ(図12)。一つは、縦方向にメモリセルを積層することである。もう一つは、X-Y方向にメモリセルをスケーリングすることである。

図12 X-Y Scalingを続けるとCMOS回路も微細化される 出所:Lars Heineck and Jin Liu(Micron), “3D NAND Flash Status and Trends”, IMW2022, Presentation Slide.

図12 X-Y Scalingを続けるとCMOS回路も微細化される 出所:Lars Heineck and Jin Liu(Micron), “3D NAND Flash Status and Trends”, IMW2022, Presentation Slide.前者では、ARの高い孔の加工や下段と上段の孔合わせなどが年々、困難さを増していく。一方、後者は、縦方向にメモリセルを指数関数的に積層することを緩和してくれる武器になる。

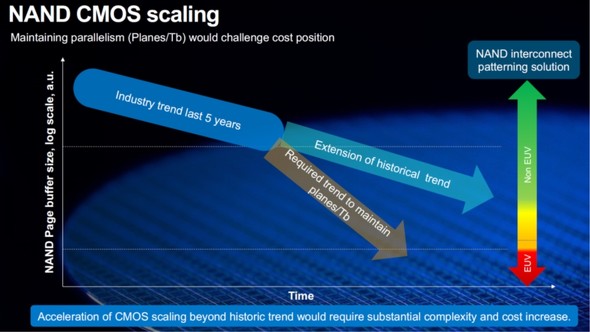

しかし、X-Y方向のスケーリングを続けると、CMOSの微細化を続けることになり、例えば、トランジスタにFinFETを使ったり、微細配線にEUVを適用したりするということにもなりかねない(図13)。これらは、メモリコストの高騰につながるため、安易に採用することはできない。

図13 CMOSの微細化が続くと配線にEUVを使うことに? 出所:Lars Heineck and Jin Liu(Micron), “3D NAND Flash Status and Trends”, IMW2022, Presentation Slide.

図13 CMOSの微細化が続くと配線にEUVを使うことに? 出所:Lars Heineck and Jin Liu(Micron), “3D NAND Flash Status and Trends”, IMW2022, Presentation Slide.従って、X-Y方向のスケーリングを行う際には、ビット当たりのCMOS回路を減らす工夫をすることが、FinFETやEUVの使用など、高価なプロセスを回避するために必要になってくる。

以上をまとめると、今後の3D NANDの高密度化には、縦方向への積層化、X-Y方向のスケーリング、ビット当たりのCMOS回路の削減、この3つの手法が重要であると言える。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待