フラッシュメモリ、NOR型に続いてNAND型が表舞台に(1980年代後半):福田昭のストレージ通信(221) フラッシュメモリと不揮発性メモリの歴史年表(5)(1/2 ページ)

今回は、1985年から1988年の主な出来事を報告する。NORフラッシュに続き、NANDフラッシュが表舞台に登場する。

東芝とエクセルマイクロエレクトロニクスのNOR型セル

フラッシュメモリに関する世界最大のイベント「フラッシュメモリサミット(FMS:Flash Memory Summit)」の会場では最近、「Flash Memory Timeline」の名称でフラッシュメモリと不揮発性メモリの歴史年表を壁にパネルとして掲げるようになっていた。現在は、FMSの公式サイトからPDF形式の年表をダウンロードできる(ダウンロードサイト)。

この年表は1952年〜2020年までの、フラッシュメモリと不揮発性メモリに関する主な出来事を記述していた。とても参考になるので、その概略をシリーズで説明する。なお原文の年表は全て英文なので、これを和文に翻訳するとともに、参考となりそうな情報を追加した。また年表の全ての出来事を網羅しているわけではないので、ご了承されたい。

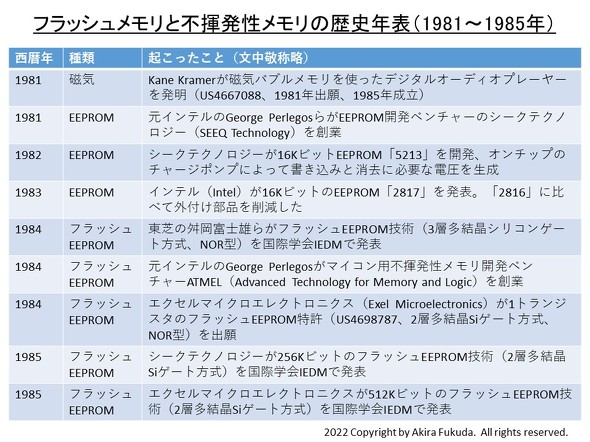

前回は、1981年から1985年の主な出来事を解説した。電気的にデータを書き換え可能な不揮発性メモリ、具体的にはEEPROM(Electrically Erasable and Programmable Read-Only Memory EEPROM)の開発が活発化し、その低コスト品であるフラッシュEEPROMが登場した年代だ。今回は、1985年から1988年の主な出来事をご報告する。

前回では、フラッシュEEPROM(以降は「フラッシュメモリ」と表記)の発明企業が少なくとも2つあると述べた。1社は日本の東芝、もう1社は米国のエクセルマイクロエレクトロニクス(Exel Microelectronics)である。両社が開発したメモリセルの構造はかなり違う。

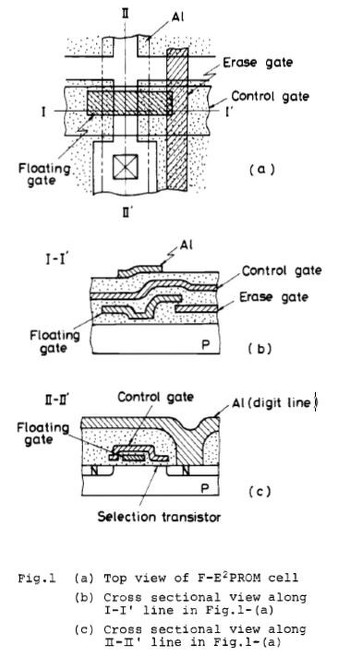

東芝が1984年12月に国際学会IEDMで発表したフラッシュメモリのメモリセルは「トリプルポリシリコン(3層多結晶シリコン)」タイプとも呼ばれる。1個のトランジスタ(MOSFET)が浮遊ゲート(電荷の蓄積用)と制御ゲート(浮遊ゲートの電位制御用)のほか、消去ゲートを備える。消去ゲートがあるため、通常のEPROMとは異なる3層の多結晶シリコンプロセスを必要とする。また制御ゲートの一部は基板(チャンネル)と重なっており、選択トランジスタとして働く。

東芝が1984年12月に国際学会IEDMで発表したフラッシュメモリのセル構造。上はレイアウト。中央は制御ゲートに沿った方向の断面構造、下はビット線に沿った方向の断面構造。IEDMの論文集から(論文番号17.3)[クリックで拡大]

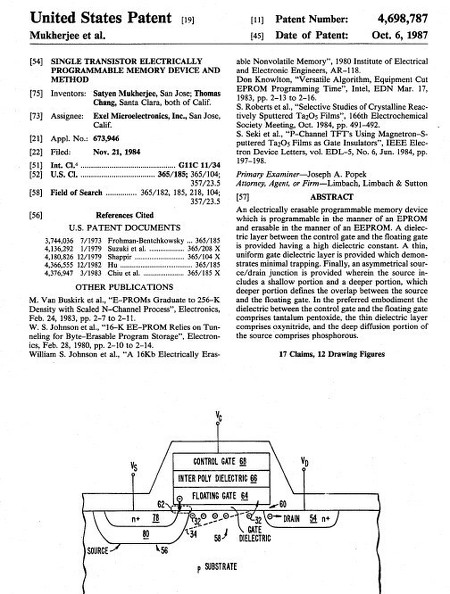

東芝が1984年12月に国際学会IEDMで発表したフラッシュメモリのセル構造。上はレイアウト。中央は制御ゲートに沿った方向の断面構造、下はビット線に沿った方向の断面構造。IEDMの論文集から(論文番号17.3)[クリックで拡大]エクセルマイクロエレクトロニクスが1984年11月に米国特許(US4698787)を出願したメモリセルは、EPROMと同様の2層多結晶シリコンプロセスで作る。浮遊ゲートの一部は拡散層と重なっており、消去動作では浮遊ゲートから拡散層に電荷を引き抜く。

データの書き換え原理は、両社とも同じである。書き込み(浮遊ゲートへの電子注入)にはホットエレクトロン効果、消去(浮遊ゲートからの電子引き抜き)にはファウラーノルドハイム(FN:Fowler-Nordheim)トンネリング(FNトンネリング)を使う。セルアレイはいずれもNOR型である。

量産化されたNOR型フラッシュメモリ(以降は「NORフラッシュ」と表記)に近い構造は、エクセルマイクロエレクトロニクスの発明したセルだ。しかし当時の酸化膜形成技術では、極めて薄い酸化膜をチャンネル領域全体に均一に作ることは容易ではない。このため、同社が開発したセル構造の大容量メモリは、製造歩留まりを高められないとの懸念が強かった。

東芝が開発したセル構造は、消去ゲートを設けることで製造歩留まりの懸念を減らしている。しかしトリプルポリシリコンのプロセスが工程数(マスク数)を増やす、メモリセル面積が大きめになるといった弱点を抱えていた。

現実には、エクセルマイクロエレクトロニクスと類似の2層多結晶シリコン浮遊ゲート構造のセルトランジスタで、インテル(Intel)が「ETOX(EPROM Tunnel OXide)」と呼ぶ薄いゲート酸化膜の量産化に成功したことで、インテルが技術的にも商業的にもNORフラッシュの主役となっていく。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- デンソー、ロームに対する株式取得提案を正式表明

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響

- 次世代パワー半導体 「期待の5材料」の現在地――電子版2026年3月号