EE Times Japan >

LSI >

AMDが開発したサーバ向けプロセッサ「第4世代EPYC」の概要:福田昭のデバイス通信(372)(2/3 ページ)

» 2022年11月22日 11時30分 公開

[福田昭,EE Times Japan]

チップレット構成によって低コストと高性能を両立

第4世代EPYCのマイクロプロセッサはシングルダイではない。前世代のEPYCと同様に、チップレット構成を採用する。CPUコアとキャッシュを内蔵する複数のミニダイ(CCD:CPU Compute DieあるいはCore Complex Die)と、ミニダイ間接続および外部入出力を一手に担う入出力ダイ(「IO die」あるいは「IOD」)を1枚のパッケージ基板(樹脂基板)にならべた。

第4世代EPYCのパッケージ基板(表面)。2022年11月10日(米国時間)に新製品発表会「together we advance_data centers」のプレス向け説明会場で筆者が撮影したもの。中央が入出力ダイ(IOダイ)。TSMCの6nmプロセスで製造した。左右の4箇所に配置したミニダイがCCD(CPU Compute DieあるいはCore Complex Die)。こちらはTSMCの5nm FinFETプロセスで製造した。1箇所に3枚のCCDを近接してならべている。CCDの合計は12枚である。1枚のCCDは8個のZen4コア(CPUコア)とCPUコアごとの2次キャッシュ、CPUコアが共有する3次キャッシュ、入出力ダイとの接続リンクなどを内蔵する[クリックで拡大]

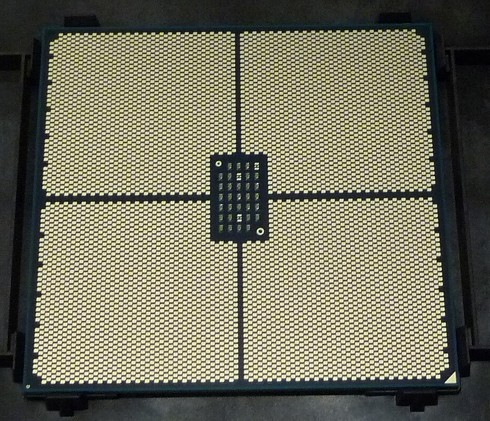

第4世代EPYCのパッケージ基板(表面)。2022年11月10日(米国時間)に新製品発表会「together we advance_data centers」のプレス向け説明会場で筆者が撮影したもの。中央が入出力ダイ(IOダイ)。TSMCの6nmプロセスで製造した。左右の4箇所に配置したミニダイがCCD(CPU Compute DieあるいはCore Complex Die)。こちらはTSMCの5nm FinFETプロセスで製造した。1箇所に3枚のCCDを近接してならべている。CCDの合計は12枚である。1枚のCCDは8個のZen4コア(CPUコア)とCPUコアごとの2次キャッシュ、CPUコアが共有する3次キャッシュ、入出力ダイとの接続リンクなどを内蔵する[クリックで拡大] 第4世代EPYCのパッケージ基板(裏面)。撮影日時と場所は上と同じ。膨大な数の電極を千鳥格子状にならべたLGA(Land Grid Array)タイプのパッケージである。電極のピッチは0.94mm×0.81mmとかなり狭い。パッケージ基板の大きさは72mm×75.4mm。ソケットは「SP5タイプ」とAMDが呼称するLGAパッケージ用ソケット[クリックで拡大]

第4世代EPYCのパッケージ基板(裏面)。撮影日時と場所は上と同じ。膨大な数の電極を千鳥格子状にならべたLGA(Land Grid Array)タイプのパッケージである。電極のピッチは0.94mm×0.81mmとかなり狭い。パッケージ基板の大きさは72mm×75.4mm。ソケットは「SP5タイプ」とAMDが呼称するLGAパッケージ用ソケット[クリックで拡大]「EPYC 9004シリーズ」の各品種は、CCDの枚数を変えることによってCPUコアの数を調整している。例えば最大32コアまでは4枚のCCD、最大64コアまでは8枚のCCD、最大96コアまでは12枚のCCDをパッケージ基板に載せる。入出力ダイ(IOD)は常に1枚である。

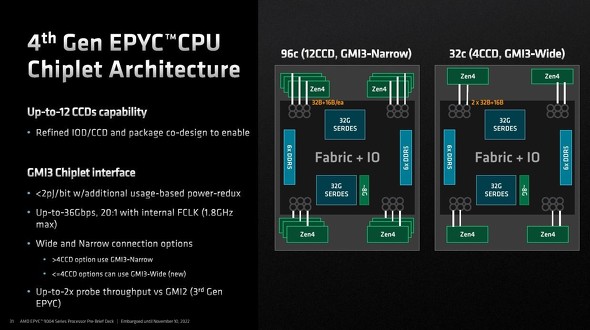

CCD(Computeダイ)とIOD(入出力ダイ)の間は、「GMI(Global Memory Interconnect)」あるいは「IFOP(Infinity Fabric On-Package)」と呼ぶバスで接続する。GMIのバス幅は32バイト+16バイトとかなり広く、最大で36Gbpsのデータ転送速度を備える。特にCCDが4枚以下の場合はGMIのバス幅が64バイト(32バイト×2チャンネル)+16バイトとさらに広がり、データ転送速度は最大で72Gbpsと倍増する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

Special SitePR

あなたにおすすめの記事PR