EE Times Japan >

LSI >

AMDが開発したサーバ向けプロセッサ「第4世代EPYC」の概要:福田昭のデバイス通信(372)(3/3 ページ)

» 2022年11月22日 11時30分 公開

[福田昭,EE Times Japan]

プロセッサの基本構成は2ソケットあるいは1ソケット

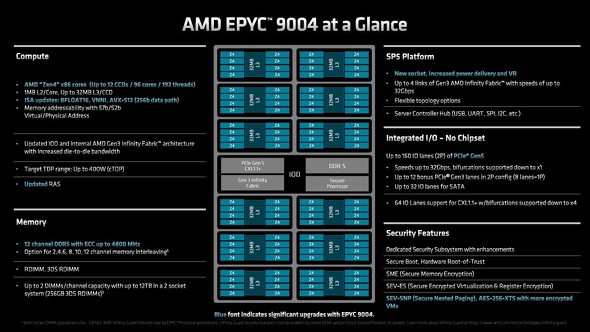

「EPYC 9004シリーズ」が前世代(第3世代)のEPYCシリーズと大きく異なる点は、新開発のZen4コアを搭載したこと、主記憶(メインメモリ)にDDR5メモリを採用するとともに接続数を12チャンネルと拡大して高速かつ大容量にしたこと、入出力インタフェースにPCIe Gen5を採用して高速化するとともにメモリ拡張インタフェースの「CXL(Compute Express Link)」に対応したこと、などだ。

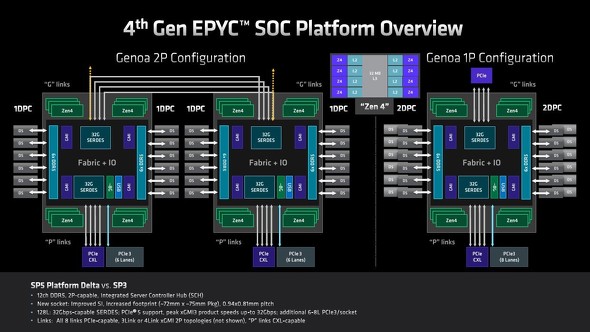

そしてマルチプロセッサの基本構成(プラットフォーム)としては、2個のSP5ソケットによって2個のCPUが対を成す「2P」構成と、1個のSP5ソケットによる「1P」構成を用意した。

「2P」構成と「1P」構成では、メモリサブシステムが大きく変わってくる。「2P」構成の場合、1チャンネルのDDR5インタフェースに接続するDIMMは1枚(1DPC:1DIMM Per Channel)となる。「1P」構成では1チャンネルのDDR5インタフェースにはDIMMを2枚(2DPC)接続できる。

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

AMD、サーバ向け高性能プロセッサ「第4世代EPYC」の第1弾を発表

AMD、サーバ向け高性能プロセッサ「第4世代EPYC」の第1弾を発表

AMDは2022年11月10日(米国時間)に米国カリフォルニア州サンフランシスコで新製品発表会「together we advance_data centers」を開催し、サーバ向けプロセッサの新製品「EPYC 9004シリーズ」の販売を開始した。 HDD大手Western Digitalの業績、フラッシュの値下がりで営業利益が前年の3分の1に減少

HDD大手Western Digitalの業績、フラッシュの値下がりで営業利益が前年の3分の1に減少

米Western Digitalの「2023会計年度第1四半期」(2022年7月〜9月)を紹介する。 携帯型MP3プレーヤーの黎明期(1997年〜1998年)

携帯型MP3プレーヤーの黎明期(1997年〜1998年)

今回はフラッシュメモリを記憶媒体とする携帯型デジタルオーディオプレーヤー(DAP:Digital Audio Player)を扱う。時期は1997年〜1998年である。 ワイヤレス電力伝送で実際に電子機器を動作させる

ワイヤレス電力伝送で実際に電子機器を動作させる

今回は「7.4 試作例」の講演パートを解説する。ワイヤレス受電端末を試作し、低消費電力の小型機器をワイヤレス電力伝送で動かした。 ワイヤレス受電用端末の試作に向けたアンテナの設計作業

ワイヤレス受電用端末の試作に向けたアンテナの設計作業

今回は「7.2 アンテナ」と「7.3 アンテナの集積化」の内容について、簡単に解説する。 ワイヤレス電力伝送の過去から未来までを展望

ワイヤレス電力伝送の過去から未来までを展望

今回から、「IEDM 2021」でオランダimec Holst Centreでシニアリサーチャー、オランダEindhoven University of TechnologyでフルプロフェッサーをつとめるHubregt J. Visser氏が講演した「Practical Implementation of Wireless Power Transfer(ワイヤレス電力伝送の実用的な実装)」の内容を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

Special SitePR

あなたにおすすめの記事PR