AMDが開発した「Zen4」CPUダイのメモリ構成:福田昭のデバイス通信(374)(1/2 ページ)

今回は「Zen4」コアを内蔵するダイ(CCD:Core Complex Die)のメモリ構成をご紹介する。

「Zen4」では「Zen3」から2次キャッシュの容量を倍増

AMDは2022年11月10日(米国時間)に米国カリフォルニア州サンフランシスコでサーバ向けプロセッサ「EPYC(エピック)」の新製品発表会「together we advance_data centers」を開催した。新しい「EPYC」は、x86互換のCPUコア「Zen(ゼン)」シリーズの第4世代となる最新のCPUコア「Zen4」を搭載する。名称は「第4世代(4th Gen)EPYC」である。筆者は幸い、新製品発表会に招待された。そこで本コラムの第371回から、第4世代EPYCの初製品「EPYC 9004シリーズ」とCPUコア「Zen4」の概要を紹介している。

本コラムの前回は、CPUコア「Zen4」の概要をご説明した。前回はマイクロアーキテクチャや回路レイアウトなどを紹介した。今回は「Zen4」コアを内蔵するダイ(CCD:Core Complex Die)のメモリ構成を簡単にご紹介する。

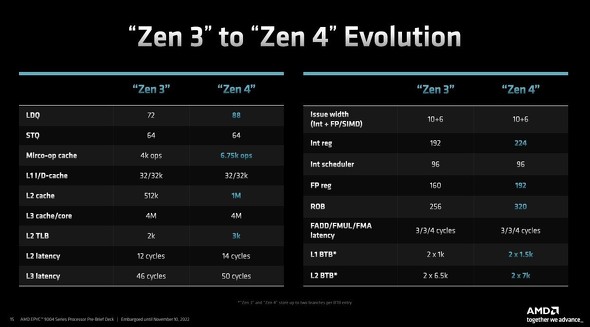

前世代の「Zen3」コアを搭載したCCDと「Zen4」コアを搭載したCCDはいずれも、3次までのキャッシュ(L3キャッシュ)を内蔵する。1次キャッシュ(L1キャッシュ)はCPUコア内にあり、命令キャッシュとデータキャッシュに分かれている。記憶容量はいずれも32Kバイトで、Zen3コアから変わっていない。

2次キャッシュ(L2キャッシュ)は、CPUコアごとに用意した。命令とデータが混在するユニファイドキャッシュである。記憶容量はZen3では512KバイトだったのがZen4では2倍の1Mバイトに増加した。なお、各コアは同時マルチスレッディング(SMT)をサポートする。具体的には最大で2つのスレッドを並行して実行する。各スレッドは2次キャッシュを共有しており、独立に動く。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待