EE Times Japan >

LSI >

AMDが開発した「Zen4」CPUダイのメモリ構成:福田昭のデバイス通信(374)(2/2 ページ)

» 2022年12月02日 11時30分 公開

[福田昭,EE Times Japan]

EPYCプロセッサの3次キャッシュ容量は前世代の1.5倍に拡大

3次キャッシュ(L3キャッシュ)あるいはラストレベルキャッシュ(LLC)は、CCDの各CPUコアが共有するシェアードキャッシュである。CPUコア当たりの記憶容量は4Mバイトで、Zen3と変わらない。CCDはZen3とZen4ともに8個のCPUコアを搭載する。このため、CCDが内蔵する3次キャッシュの記憶容量は32Mバイトのままである。

Zen4プロセッサの3次キャッシュ(ラストレベルキャッシュ)は各CPUコアが共有する。記憶容量はCPUコア当たりで4Mバイトであり、全体では32Mバイトとなる。なお「CCX(Core Complex)」はCPUコアと2次キャッシュ、3次キャッシュをまとめたマクロ(IP)を意味する。外部とやりとりする入出力回路をCCXに加えたシリコンダイ(ミニダイあるいはチップレット)が「CCD(Core Complex Die)」である[クリックで拡大] 出所:AMD

Zen4プロセッサの3次キャッシュ(ラストレベルキャッシュ)は各CPUコアが共有する。記憶容量はCPUコア当たりで4Mバイトであり、全体では32Mバイトとなる。なお「CCX(Core Complex)」はCPUコアと2次キャッシュ、3次キャッシュをまとめたマクロ(IP)を意味する。外部とやりとりする入出力回路をCCXに加えたシリコンダイ(ミニダイあるいはチップレット)が「CCD(Core Complex Die)」である[クリックで拡大] 出所:AMDただし第4世代EPYCは1個のプロセッサが最大で12枚のCCDを搭載する。第3世代EPYCが最大で8枚であったから、プロセッサが搭載可能な3次キャッシュの記憶容量は第3世代EPYCの256Mバイトから、第4世代EPYCでは384Mバイトと1.5倍に拡大した。

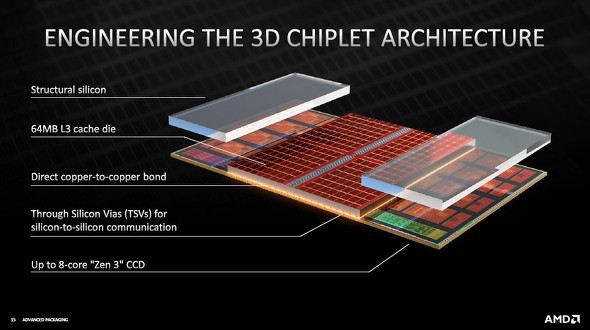

なお前世代(第3世代)のEPYCプロセッサは、CCD当たりの3次キャッシュをシリコンダイ積層技術によって96Mバイトに拡大できた。CCDと、64Mバイトの3次キャッシュダイをハイブリッド接合技術によって積層する。AMDはこの技術を「3D V-Cache」と呼んでいる。この技術を採用した第3世代EPYCプロセッサは最大で768Mバイトと巨大な3次キャッシュを備える。

64Mバイトの3次キャッシュダイをハイブリッド接合技術によってCCDと積層する「3D V-Cache」の構造図[クリックで拡大] 出所:AMDが2021年8月22日に国際学会「Hot Chips 33」のチュートリアルセッションで発表したスライド

64Mバイトの3次キャッシュダイをハイブリッド接合技術によってCCDと積層する「3D V-Cache」の構造図[クリックで拡大] 出所:AMDが2021年8月22日に国際学会「Hot Chips 33」のチュートリアルセッションで発表したスライド⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

AMDが開発した第4世代のZenコア「Zen4」の概要

AMDが開発した第4世代のZenコア「Zen4」の概要

今回は、Zenアーキテクチャのx86互換64ビットCPUコアで第4世代となる「Zen4」の概要をご紹介する。 AMD、サーバ向け高性能プロセッサ「第4世代EPYC」の第1弾を発表

AMD、サーバ向け高性能プロセッサ「第4世代EPYC」の第1弾を発表

AMDは2022年11月10日(米国時間)に米国カリフォルニア州サンフランシスコで新製品発表会「together we advance_data centers」を開催し、サーバ向けプロセッサの新製品「EPYC 9004シリーズ」の販売を開始した。 HDD大手Western Digitalの業績、フラッシュの値下がりで営業利益が前年の3分の1に減少

HDD大手Western Digitalの業績、フラッシュの値下がりで営業利益が前年の3分の1に減少

米Western Digitalの「2023会計年度第1四半期」(2022年7月〜9月)を紹介する。 HDD大手Seagateの四半期業績は2桁%の減収減益に

HDD大手Seagateの四半期業績は2桁%の減収減益に

米Seagate Technologyの2023会計年度第1四半期(2022年7月〜9月)の業績を紹介する。 携帯型MP3プレーヤーの黎明期(1997年〜1998年)

携帯型MP3プレーヤーの黎明期(1997年〜1998年)

今回はフラッシュメモリを記憶媒体とする携帯型デジタルオーディオプレーヤー(DAP:Digital Audio Player)を扱う。時期は1997年〜1998年である。 ビデオカメラの記録媒体にフラッシュメモリが進出(2003年〜2004年)

ビデオカメラの記録媒体にフラッシュメモリが進出(2003年〜2004年)

今回は、動画記録用の媒体にフラッシュメモリを利用したデジタルビデオカメラを報告する。年表の時期は2003年〜2004年である。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

Special SitePR

あなたにおすすめの記事PR