EE Times Japan >

先端技術 >

アナログCIM回路でCNNとTransformerの処理を実現:容量再構成型CIM構造を提案(2/2 ページ)

» 2024年02月27日 13時30分 公開

[馬本隆綱,EE Times Japan]

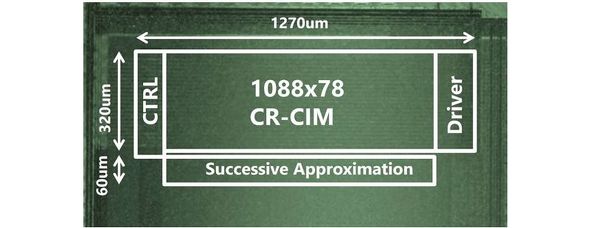

TSMCの65nmプロセスでCIMを試作

実験では、TSMCの65nmプロセスを用いて、CIMを設計/試作した。試作したチップの性能を評価したところ、Transformerモードで最大1.2TOPS、ピーク電力効率で818TOPS/Wを達成。CNNモードでは最大6TOPS、ピーク電力効率は4094TOPS/Wとなり、同等の演算精度を持つCIMに比べ、電力効率は10倍高くなることが分かった。

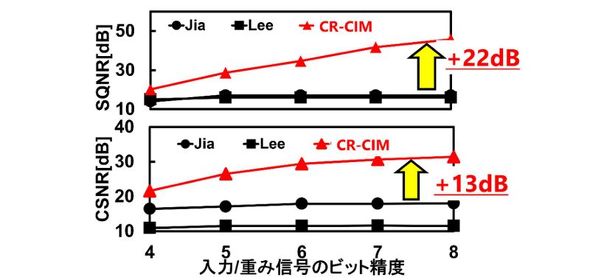

従来のアナログCIMに比べ、量子化雑音比(SQNR)は22dB高く、演算精度(CSNR)は13dB高い性能となった。こうしたことから、効率が高く、Transformerでも十分な計算精度を実現した。アルゴリズムではVision Transformer(ViT-S)モデルを用いた時に、CIFAR10データセットで95%という高い正答率になることを確認した。高効率のCNNモードを用いた場合、Resnet-20モデルで同データセットにて91%の精度を達成した。

今回の研究成果については、2024年2月18日より米国で開催された「ISSCC 2024(国際固体素子回路会議)」で詳細を発表した。

関連記事

フレキシブル基板上の磁性薄膜で創発インダクタンスを観測

フレキシブル基板上の磁性薄膜で創発インダクタンスを観測

慶應義塾大学とブラウン大学、中国科学院大学らの共同研究チームは、フレキシブル基板上の磁性薄膜において、室温かつ低磁場の環境で「創発インダクタンス」を観測し、そのメカニズムについても解明した。 ナノ半導体間界面で「エネルギー共鳴現象」を発見

ナノ半導体間界面で「エネルギー共鳴現象」を発見

理化学研究所(理研)と筑波大学、東京大学、慶應義塾大学らの共同研究グループは、異なる次元性を持つナノ半導体間の界面で、バンドエネルギー共鳴により励起子移動が増強する現象を発見した。 相変化メモリ向け新材料「テルル化ニオブ」を発見

相変化メモリ向け新材料「テルル化ニオブ」を発見

東北大学の研究グループは、産業技術総合研究所や慶應義塾大学とともに、相変化メモリ(PCRAM)の電力消費を大幅に抑え、高速動作や高温環境での使用を可能にする相変化材料として、二次元層状物質の「テルル化ニオブ(NbTe4)」を発見した。 双極子の荷電π電子系を積層した集合体を形成

双極子の荷電π電子系を積層した集合体を形成

立命館大学は、京都大学や慶應義塾大学、近畿大学、愛媛大学、JSRと共同で、双極子を有するπ電子系カチオンを同種電荷種間で積層し、集合化形態に起因する物性の変調や、半導体特性の発現が可能であることを解明した。 マグネシウム蓄電池向けの酸化物正極材料を開発

マグネシウム蓄電池向けの酸化物正極材料を開発

東北大学や慶應義塾大学などの研究チームは、マグネシウム蓄電池の正極材料として、スピネル型のマグネシウムマンガン系酸化物を開発した。 ローム、オンデバイス学習AIチップを開発

ローム、オンデバイス学習AIチップを開発

ロームは、消費電力が数十ミリワットと極めて小さく、エッジ側で「学習」と「推論」の両方を行うことができる「オンデバイス学習AIチップ」を開発した。クラウドサーバとの連係がなくても、エッジ側だけでリアルタイムに故障予知を行うことができるという。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR