AIは、シリコンフォトニクスのキラーアプリになるのか?:業界のキープレイヤーが議論(2/3 ページ)

パッケージングとEDAが議題の中心に

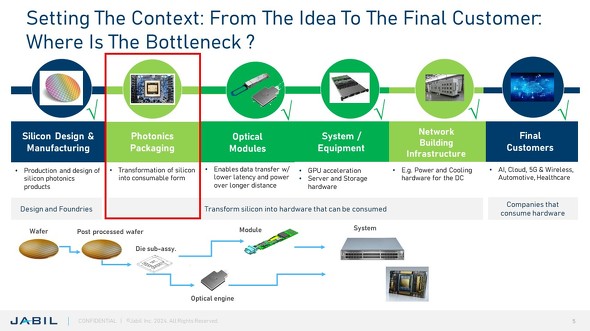

今回のプレゼンテーションでは、シリコンフォトニクスが現在転換点にあるということが明らかになった。しかし、スケーリングやエネルギー効率、パッケージング、エコシステムの他、EDAやサードパーティーIP(Intellectual Property)のようなツール、材料などに関しては、まだ課題が残っている。

特に議論の中心となったのは、パッケージングとEDAだ。

Jabilでプロダクトマネジメント/開発部門担当ディレクターを務めるGiorgio Cazzaniga氏は、「パッケージングに関しては、大規模な生産能力体制を確立してフォトニクスパッケージングプロセスを構築する必要がある。現在、シリコンフォトニクスの市場参入コストが低いのは、試作用のパイロットラインを利用できているからだ」と述べる。

Cazzaniga氏は、「AIの数量を満たすために、何千、何百万個もの生産にソリューションが必要な場合はどうなるのだろうか」と問いかけた。

同氏は、シリコンフォトニクスのパッケージングプロセスとチップレットの共通性について指摘する。

「チップレットアーキテクチャは、メモリやコンピューティング、アクセラレーションなどのさまざまなタスク向けに特化した技術で設計された、異なる種類のチップを、同じインターポーザー上に搭載できる可能性を提供する。チップレットはPIC(フォトニック集積回路)として、他のものと同じ基板上に統合できる。パッケージングの観点から見ると、チップレットアーキテクチャは、フリップチップやボンディングなどのいくつかのステップを必要とする。これらのステップは、フォトニクスパッケージング活動にも必要だ。しかしフォトニクスチップには、ファイバー接続のような専用のステップが必要だ」(Cazzaniga氏)

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 加賀電子が新光商事にTOB、完全子会社化へ

- SiC LSIの事業化に挑む 28年以降ADCのサンプル出荷へ

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- Cerebrasが上場 NVIDIA対抗馬の「試金石」となるか

- AIの「トンデモ判断」で本番DBが全飛び! 他山の石にしたいAIコーディングの落とし穴

- サンケン電気26年3月期は赤字転落 中国の「自前主義」響く

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略