寄生発振抑制と高速スイッチングを両立、東芝のSiCモジュール:小さいゲート抵抗で発振抑制

東芝デバイス&ストレージ(以下、東芝D&S)と東芝は、SiCーMOSFETを搭載したパワーモジュールの寄生発振を抑制する独自技術を開発した。【修正あり】

配線レイアウトを最適化することで抑制

東芝デバイス&ストレージ(以下、東芝D&S)と東芝は、SiCーMOSFETを搭載したパワーモジュールの寄生発振を抑制する独自技術を開発した。寄生発振はゲート抵抗を用いて抑制する手法が一般的だが、配線レイアウトを最適化することで抑制するもの。ゲート抵抗を大きくすることで生じるスイッチング速度の低下などなく、寄生発振を抑えられる。同技術は2024年6月に開催されたパワー半導体の国際学会「The 36th International Symposium on Power Semiconductor Devices and ICs(ISPSD)2024」で発表された。

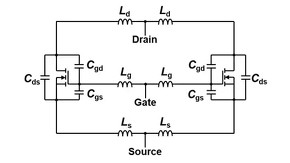

複数のチップを並列接続するSiCパワーモジュールは、チップ間の配線インダクタンスやチップ寄生容量によって発振回路が形成され、寄生発振が生じる。寄生発振は、モジュールの信頼性に影響を及ぼすため、抑制する必要がある。寄生発振を抑える手法としては、ゲート抵抗を用いることが一般的になっている。ただ、大きなゲート抵抗を用いると、スイッチング速度の低下、スイッチング損失の増大を招くというトレードオフを抱える。

パワーモジュールは、スイッチング速度が速いほど、トランス、コンデンサーなど周辺部品を小型化でき、電力変換システムを小さくできる。そのため、小さいゲート抵抗でスイッチング速度を犠牲にせずに寄生発振を抑制する技術が求められている。

従来比60%小さいゲート抵抗で抑制可能に

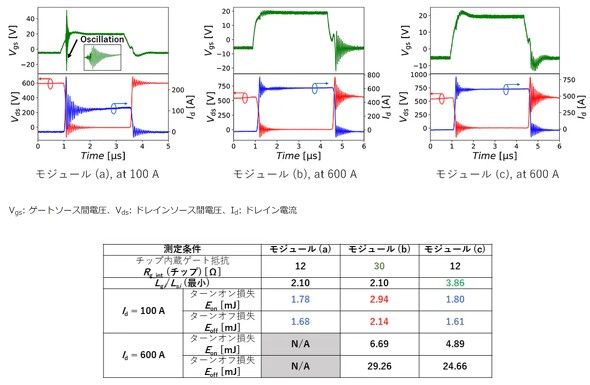

東芝グループが開発した技術は、寄生発振が生じにくい配線レイアウトで、ゲート抵抗を用いた発振抑制手法と比較して60%小さいゲート抵抗でも発振を抑制できるというもの。パワーモジュールの等価回路モデルから寄生発振が生じる条件を理論的に導出。並列接続されたチップのゲート間インダクタンスLgとソース間インダクタンスLsの比率(=Lg/Ls)がある一定値以下となった場合に寄生発振することを解析で導き出した。解析結果に基づき、Lg/Lsが異なるモジュールを試作し、スイッチング試験を実施。その結果、Lg/Lsを大きくすると小さいゲート抵抗でも発振を抑制できることを確認した。

【訂正:2024年8月5日14:50 「2並列MOSFETの等価回路モデル」の図版につきまして、東芝のプレスリリースにおける回路図差し替えに伴い、本記事内の図版も変更しております。】

東芝グループでは「今回開発した寄生発振の抑制手法を開発中のパワーモジュールに適用することで、小さなゲート抵抗でも寄生発振を生じにくく、低損失かつ、発振を抑制し高信頼なスイッチング動作が可能なパワーモジュールを提供することが可能になる。今後、さらなる改良を進め、早期実用化を目指す」としている。

関連記事

2023年SiCパワーデバイス世界売上高ランキング、首位はST

2023年SiCパワーデバイス世界売上高ランキング、首位はST

市場調査会社のTrendForceはSiCパワーデバイス市場についての調査を発表した。それによると、2023年の市場シェアはSTMicroelectronicsが32.6%を占めて首位となり、onsemiは23.6%で前年の4位から2位に浮上した。続くInfineon Technologies、Wolfspeed、ロームを含めた上位5社が総売上高の91.9%を占めていたという。 ロームの独子会社がSiCウエハー新棟を起工、生産能力3倍目指し

ロームの独子会社がSiCウエハー新棟を起工、生産能力3倍目指し

ローム子会社でSiCウエハー製を手掛けるドイツSiCrystalが、ドイツ・ニュルンベルクにおいて、SiCウエハーの生産能力拡大に向けた新棟を起工した。2026年初旬に完成予定で、既存施設も含めたSiCrystal全体の生産能力は2027年に3倍(2024年比)になる予定だという。 スイッチング損失を従来比で30%低減したSiCモジュール

スイッチング損失を従来比で30%低減したSiCモジュール

日立パワーデバイスは2021年12月21日、鉄道車両や再生可能エネルギー発電システム向けに、耐圧1.7kVのフルSiCモジュールを開発したと発表した。同社の従来品に比べて、スイッチング損失を約30%低減したことが特長となる。 第9回 発振回路を評価する3つの作業〜発振余裕度と励振レベル〜

第9回 発振回路を評価する3つの作業〜発振余裕度と励振レベル〜

今回は、前回紹介した周波数マッチング(発振周波数精度)の評価に続いて、発振余裕度(負性抵抗)と励振レベル(ドライブレベル)の評価に移りましょう。 東芝D&S、耐圧2200VのSiC MOSFETを開発

東芝D&S、耐圧2200VのSiC MOSFETを開発

東芝デバイス&ストレージ(東芝D&S)は、耐圧2200VのSiC(炭化ケイ素)MOSFETを開発した。太陽光発電(PV)用インバーターシステムの小型軽量化が可能になる。【訂正あり】 サンケン電気、スイッチング電源用パワーICを量産

サンケン電気、スイッチング電源用パワーICを量産

サンケン電気は、パワーMOSFETと電流モード型PWM制御ICを1パッケージに集積したPWM型スイッチング電源用パワーIC「STR6A153MVD」を開発、量産を始めた。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増