磁場履歴を記憶できる巨大抵抗変化メモリを実現:磁気抵抗比は最大で3万2900%

東京大学の研究グループは、産業技術総合研究所や広島大学、海洋研究開発機構と共同で、印加された磁場の履歴を記憶でき、これを巨大な抵抗変化として読み出せるメモリ(メモリスタ)を実現した。

メモリスタの磁場依存性と印加電圧の履歴依存性を組み合わせて実現

東京大学の研究グループは2025年1月、産業技術総合研究所や広島大学、海洋研究開発機構と共同で、印加された磁場の履歴を記憶でき、これを巨大な抵抗変化として読み出せるメモリ(メモリスタ)を実現したと発表した。今回は、最大で3万2900%の磁気抵抗比が得られたという。この値はMRAM素子の30〜100倍に相当する。

メモリスタは、入力電圧の履歴に基づいて抵抗が変化するデバイスで、次世代メモリやインメモリコンピューティング、ニューロモルフィックコンピューティングなどへの応用が期待されている。

メモリスタは一般的に、絶縁層を金属電極層で挟んだ二端子デバイスで構成される。これまで、電圧でメモリスタの抵抗を制御する研究は行われてきたが、メモリスタの磁場依存性に関する報告は、あまりなかったという。

研究グループは今回、コバルト(Co)や鉄(Fe)、酸化マグネシウム(MgO)、ボロン添加Ge(Ge:B)および、Geからなる多層膜を電極とし、n型半導体ゲルマニウム(n--Ge)をチャネルとする二端子デバイスを作製した。

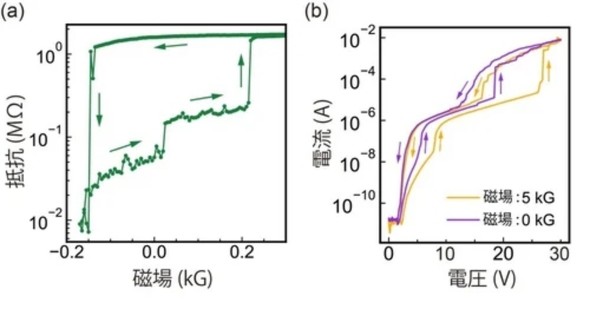

実験では、3Kという低温環境の中で、開発した二端子デバイスに一定の電圧を印加し、外部磁場の大きさを変えたところ、抵抗が大きく変化することを確認した。素子が低抵抗になった状態で磁場の掃引方向を変えた。そうすると、磁場の履歴を反映してその抵抗に近い状態が維持され、その後高抵抗状態に戻った。これらの結果から、磁場の履歴に応じて抵抗を保持できることが分かった。

開発した素子では、電流−電圧特性として特異な2段階の抵抗スイッチを検出できた。実験で得られた磁場履歴の記憶機能は、高電圧側の抵抗スイッチによるものだが、低電圧と高電圧領域のスイッチングのどちらでも、磁場によってスイッチングが起きる電圧を制御できるという。

今回生じた現象の起源としては、2つのメカニズムを想定している。一つは、「MgO層内のMg空孔がフィラメントを形成して抵抗が変わるモデル」。もう一つは「n--Geチャネル内のインパクトイオン化によるブレークダウンで、必要な電圧が上昇するモデル」である。これらの現象がそれぞれ独自に起こり、今回のような特性が得られたとみている。

今回の研究成果は、東京大学大学院工学系研究科の金田昌也大学院生、新屋ひかり特任准教授、吉田博嘱託研究員、田中雅明教授、大矢忍教授らのグループと、産業技術総合研究所の福島鉄也研究チーム長、広島大学大学院先進理工系科学研究科の武田崇仁助教、海洋研究開発機構の真砂啓技術副主幹らによるものである。

関連記事

ダイヤモンド表面を原子レベルで可視化 デバイス性能向上に貢献

ダイヤモンド表面を原子レベルで可視化 デバイス性能向上に貢献

東京大学は、産業技術総合研究所(産総研)と共同で、ダイヤモンド表面を原子レベルで可視化する技術を開発した。ダイヤモンド薄膜が成長する機構の解明や、ダイヤモンドデバイスの性能向上に貢献できるとみている。 室温で情報を読み書きできる「交代磁性体」を発見

室温で情報を読み書きできる「交代磁性体」を発見

東京大学は、室温で情報の読み書きが可能な、「交代磁性体」と呼ばれる新たな磁性体を発見した。超高密度かつ情報の読み書きが極めて速い次世代の情報媒体としての活用が期待される。 AlNパワー半導体開発加速に弾み 電流輸送機構を解明

AlNパワー半導体開発加速に弾み 電流輸送機構を解明

東京大学の研究グループと日本電信電話(NTT)は、窒化アルミニウム(AlN)系半導体を用いたショットキーバリアダイオード(SBD)を作製し、その電流輸送機構を解明した。今後、AlN系半導体を用いた低損失パワー半導体デバイスの実現に取り組む。 生体神経組織の動作を模倣するトランジスタを開発

生体神経組織の動作を模倣するトランジスタを開発

産業技術総合研究所(産総研)と東京大学、九州大学、兵庫県立大学、名古屋工業大学らによる研究グループは、生体神経組織の動作を模倣できるMOSトランジスタの動作実証に成功した。従来のCMOSトランジスタに比べ100万倍以上もゆっくり動作し、消費電力は500pWと極めて小さい。 グラフェン素子からの波長可変な赤外発光を初観測

グラフェン素子からの波長可変な赤外発光を初観測

東京農工大学の研究グループは、情報通信機構やアデレード大学、東京大学と協働し、磁場下のグラフェン素子において、波長を可変できる電気駆動の赤外発光を初めて観測したと発表した。 SiC低価格化の鍵になるか ヘテロエピ成長用「中間膜」技術

SiC低価格化の鍵になるか ヘテロエピ成長用「中間膜」技術

東京大学発のスタートアップであるGaianixx(ガイアニクス)は「CEATEC 2024」で、同社が手掛ける「多能性中間膜」の技術を展示した。ヘテロエピタキシャル成長用の技術で、さまざまな金属材料の単結晶膜をシリコン基板上に形成できるようになる。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

![実験結果から想定されるデバイスの動作原理[クリックで拡大] 出所:東京大学](https://image.itmedia.co.jp/ee/articles/2501/20/tm_250120tokyo01.jpg)