「富岳NEXT」開発が始動 GPUでNVIDIA参画、Rapidus採用の可能性も:富岳の100倍の性能を目指す(2/3 ページ)

CPUとGPUを高密度で統合 Rapidus採用の可能性も

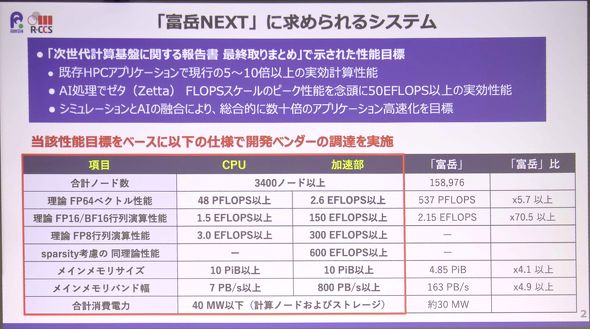

文部科学省は富岳NEXTに求められる性能については以下のように定めている。

- 既存HPCアプリケーションで現行の5〜10倍以上の実効計算性能

- AI処理でゼタFLOPSスケールのピーク性能を念頭に50EFLOPS以上の実効性能

- シミュレーションとAIの融合によって、総合的に数十倍のアプリケーション高速化

理研は、この目標を満たすための仕様を策定した。合計ノード数はCPUとアクセラレーターで計3400ノード以上、理論FP64ベクトル性能はCPUで48PFLOPS以上、アクセラレーターで2.6EFLOPS以上。理論FP16/BF16行列演算性能はCPUで1.5EFLOPS以上、アクセラレーターで150EFLOPS以上。理論FP8行列演算性能はCPUで3.0EFLOPS以上、アクセラレーターで300EFLOPS以上。sparsity考慮の同理論性能はアクセラレーターで600EFLOPS以上。メインメモリサイズはCPU/アクセラレーター共に10PiB以上。メインメモリバンド幅はCPUで毎秒7PB以上、アクセラレーターで毎秒800PB以上、合計消費電力は計算ノードおよびストレージで40MW以下だ。

この仕様をもとに、CPUとアクセラレーターの開発を主導する企業として、富士通とNVIDIAが一般競争入札で選定された。選定理由について理研は「富士通は『京』や富岳の開発における実績や今後に向けた技術的なコミットメントが高く評価された。NVIDIAは現時点で世界最高のGPUベンダーでありながら理研や富士通との共同研究をさらに推進したいという熱意があり、他社との差別化につながった」とした。

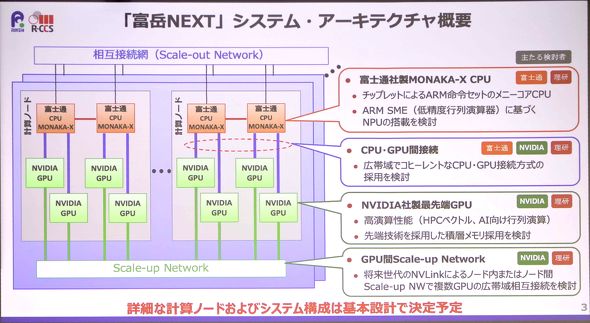

CPUには富士通が現在開発している汎用プロセッサ「FUJITSU-MONAKA」を発展させた「FUJITSU-MONAKA X」(仮称)を用いる。Arm SME(低精度行列演算器)に基づくNPUの搭載も検討する。

ここに、アクセラレーターとしてNVIDIAのGPUを高密度で統合し、計算ノードとする。接続は広帯域でコヒーレントな接続方式を検討している。GPUはNVIDIAの高性能なベクトル処理やAI向け行列演算の技術を搭載し、先端技術を活用した積層メモリの採用も検討する。GPU間のScale-up Networkとして、将来世代のNVLinkによるノード内またはノード間を接続し、複数GPUの広帯域相互接続を行うことも検討する。

CPU/GPUの製造委託先については決定していないというが、「Rapidusを活用する可能性があるか」という質問に対し、富士通 CTO(最高技術責任者)のVivek Mahajan氏は「富士通はTSMCと長年良好な関係にある一方で、『Made with Japan』という戦略においてはRapidusも重要な位置にある」とした。理研 計算科学研究センター センター長の松岡聡氏は「理研は文部科学省が所管する研究機関だが、省庁の垣根を越えた取り組みを行うことがモットーなので、(経済産業省が支援する)Rapidusも重要な位置付けだ」と述べた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長