高密度/低消費電力3D DRAMの実用化に前進 キオクシアが基盤技術を発表:メモリセル積層化によるコスト増を抑制

キオクシアは、高密度/低消費電力の3次元(3D)DRAMの実用化に向けた基盤技術として、高積層可能な酸化物半導体(InGaZnO)チャネルトランジスタを発表した。これによってAIサーバやIoT製品など幅広い用途で低消費電力化が実現する可能性がある。

キオクシアは2025年12月12日、高密度/低消費電力の3次元(3D)DRAMの実用化に向けた基盤技術として、高積層可能な酸化物半導体(InGaZnO)チャネルトランジスタを開発したと発表した。これによってAIサーバやIoT製品など幅広い用途で低消費電力化が実現する可能性がある。

同技術は、米国カリフォルニア州サンフランシスコで開催された電子素子に関する国際会議「International Electron Devices Meeting(IEDM) 2025」で発表された。

積層化によるコスト増とリフレッシュ電流の増加に対応

AIの需要が高まる中、より大きいデータを処理できる大容量かつ低消費電力のDRAMの実現が期待されている。従来のDRAMではメモリセルの微細化が物理限界に近づいていることから、さらなる大容量化に向けてメモリセルを積層する3D DRAMの研究が進んでいる。しかし、メモリセルを積層する際、トランジスタのチャネル材料として従来のDRAMと同様の単結晶シリコン(Si)を用いると、製造コストが高くなるほか、メモリ容量に比例してリフレッシュ時の電力も増加するという課題があった。

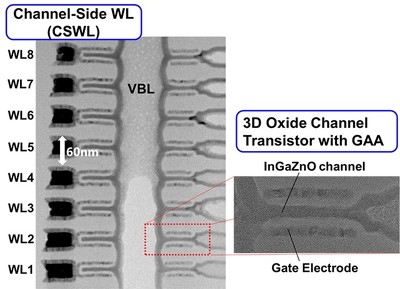

こうした課題に対してキオクシアは研究を行っていて、「IEDM 2024」では酸化物半導体の縦型トランジスタを用いたOCTRAM(Oxide-Semiconductor Channel Transistor DRAM)技術を発表していた。今回は、OCTRAMの3D化に向けて高積層可能な酸化物半導体チャネルトランジスタ技術を開発し、トランジスタを8層積層して動作することを確認した。

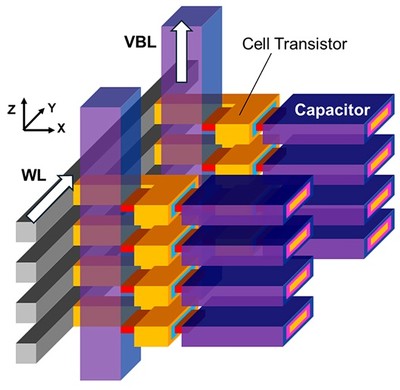

この技術では、一般的なSi酸化膜とSi窒化膜を積層膜として用い、Si窒化膜領域を酸化物半導体にリプレースすることで、縦方向に一括で横型トランジスタを形成するプロセスを採用した。同時に、縦方向のピッチのスケーリングを可能にする3Dメモリセル構造も導入した(下図)

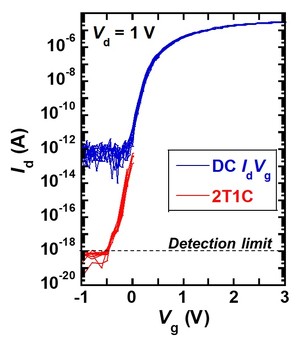

これらの製造プロセスと構造によって、メモリセルの積層化におけるコストの課題を克服することが期待される。さらに、酸化物半導体の低いオフ電流という特徴によって、リフレッシュ電力の抑制も期待できる。

キオクシアは、今後も同技術を用いた3D DRAMの実用化に向けて研究開発を進めるとしている。

関連記事

物流システムの課題解決に向けたAIソリューション、キオクシアが発表

物流システムの課題解決に向けたAIソリューション、キオクシアが発表

キオクシアは2025年12月、椿本チエインやEAGLYSと共同で、物流工程における作業効率を改善し、コスト削減が可能となるAIソシューションを開発した。新商品などが追加されてもAI再学習のための新たな作業が不要である。 キオクシアの四半期業績、売上高が前期比で4四半期ぶりに増加

キオクシアの四半期業績、売上高が前期比で4四半期ぶりに増加

今回は、キオクシアホールディングスの2025会計年度(2026年3月期)第2四半期(2025年7月〜9月期)の決算を紹介する。 キオクシアのNAND戦略 「BiCS FLASH」はどう進化するのか

キオクシアのNAND戦略 「BiCS FLASH」はどう進化するのか

キオクシアホールディングスの副社長執行役員である太田裕雄氏が、同社の主力製品である「BiCS FLASH」のロードマップやキーテクノロジー、開発中の新メモリソリューションなどについて語った。 酸化物半導体を用いた新しいDRAM技術を開発 キオクシア

酸化物半導体を用いた新しいDRAM技術を開発 キオクシア

キオクシアは、酸化物半導体(InGaZnO)トランジスタを用いて新たなDRAM技術を開発した。オフ電流が極めて少なく、従来のDRAMに比べ消費電力を低減できるという。 キオクシアとSK hynixがMRAMの大容量化技術を共同開発

キオクシアとSK hynixがMRAMの大容量化技術を共同開発

キオクシアは2024年10月21日、国際会議「IEDM 2024」において、新コンセプトの半導体メモリ技術に関する3本の論文が採択されたと発表した。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待