モノリシック集積の限界を超えるヘテロジニアス集積化:福田昭のデバイス通信(505) TSMCが解説する最新のパッケージング技術(2)

2025年12月に開催された国際学会IEDMにおける、TSMCの講演を解説するシリーズ。今回は、アウトラインの第2項である「先進パッケージ技術の進化」を取り上げる。

先進パッケージング技術の進化をたどる

2025年12月に開催された国際学会IEDMのショートコース(技術解説)で、シリコンファウンドリー最大手のTSMCが最新のパッケージング技術を説明した。講演のタイトルは「Advanced Packaging and Chiplet Technologies for AI and HPC Applications(AIおよびHPCに向けた先端パッケージング技術と先端チップレット技術)」、講演者はAdvanced Package Integration Division R&DのディレクターをつとめるJames Chen氏である。大変に参考となる内容だったので、その一部をご紹介したい。ただし講演内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演内容を筆者が適宜、補足している。あらかじめご了承されたい。

講演「Advanced Packaging and Chiplet Technologies for AI and HPC Applications(AIおよびHPCに向けた先端パッケージング技術と先端チップレット技術)」のアウトライン[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

講演「Advanced Packaging and Chiplet Technologies for AI and HPC Applications(AIおよびHPCに向けた先端パッケージング技術と先端チップレット技術)」のアウトライン[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)タイトルスライドの次に示されたアウトラインは、「AI and HPC Market Outlook(AIとHPCの市場を展望)」「Advanced Package Technology Evolutions(先進パッケージ技術の進化)」「System-Technology Co-Optimization (STCO)(システムと製造の協調最適化)」「Emerging Advanced package technology(次世代の先進パッケージ技術)」「Summary(まとめ)」となっていた。

本シリーズの初回である前回は、アウトラインの第1項「AI and HPC Market Outlook(AIとHPCの市場を展望)」に相当する部分をご報告した。今回からはアウトラインの第2項「Advanced Package Technology Evolutions(先進パッケージ技術の進化)」の概要をご紹介する。

2010年代に訪れたシステムLSI(SoC)の限界

おおよそ西暦2010年までの大規模半導体集積回路(LSI)は、1枚のシリコンダイに搭載するトランジスタの数を増やすことで、より多くの機能を取り込むとともに、動作周波数を高めることで進化してきた。システムを1枚のチップ(シリコンダイ)に収容する「システムLSI」あるいは「SoC(System on a Chip)」が標準的な考え方(「モノリシック集積」の規模拡大)だった。半導体パッケージはシリコンダイの性能を維持しながら、シリコンダイと実装基板(多くの場合はプリント基板)を電気的かつ機械的に接続する役目を負っていた。これが既存の半導体パッケージング技術(「従来パッケージング技術」)である。

ところが、「モノリシック集積」の規模拡大に伴うシリコンダイの寸法拡大(面積増大)が、いくつかの要因によって制限されるようになってきた。最も重要な問題は製造コストの急激な増加である。製造コストは粗くまとめてしまうと、1枚のウエハーから何枚のシリコンダイを生産できるかによって決まる。生産枚数が多くなると、シリコンダイ当たりの製造コストは低下する。

生産可能なシリコンダイの枚数は、シリコンダイの寸法(シリコン面積)によって決まる。シリコン面積の拡大はウエハー当たりの生産可能枚数の減少、すなわち製造コストの上昇を意味する。過去にはウエハーの口径を拡大することによって生産枚数の減少と製造コストの上昇を抑えてきた。しかしウエハーの口径(直径)は300mmが実用的な最大値となっており、次世代ウエハー(直径450mm)に移行する見込みはほぼゼロに近い。

そこで製造コストを抑えるため、意図的にシリコンダイを2つ以上に分割し、2つ以上の小さなダイ(ミニダイあるいはチップレット)をパッケージ基板にならべるという考え方(チップレット)が登場した。以前から存在していた「マルチチップパッケージ」(複数の半導体ダイを1つのパッケージに収容するもの)と「チップレット」は違う。前者は、異なるプロセス技術で製造したシリコンダイを1つのパッケージにまとめることで取り扱いを容易にするとともにプリント基板への実装面積を節約する。後者は、本来であれば(製造コストを無視すれば)容易に製造可能なシリコンダイを、わざと複数の小さなダイ(チップレット)に分割して製造コストを大きく下げる。チップレットを1つのパッケージにまとめるコストを差し引いても、全体の製造コストはシステムLSI(SoC)よりも低くなる。

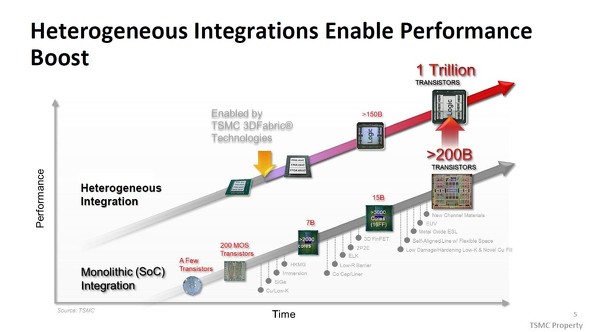

チップレットを積極的に活用すると、トランジスタ数でシステムLSI(SoC)を超えることが可能になる。またロジックだけでなく、メモリやミックスドシグナル、入出力回路などのチップレットを同じパッケージに収容することで、複数の異種ダイを集積化(ヘテロジニアス集積化)する。こうなると総合性能ではモノリシック集積のSoCをはるかに超える、ヘテロジニアス集積化モジュールが実現できる。

ヘテロジニアス集積化(先進パッケージング)技術によってモノリシック集積(SoC:システムオンチップ)の限界を超える。横軸を時間、縦軸を性能とするイメージ[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

ヘテロジニアス集積化(先進パッケージング)技術によってモノリシック集積(SoC:システムオンチップ)の限界を超える。横軸を時間、縦軸を性能とするイメージ[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)そしてヘテロジニアス集積化モジュールの高性能化と大規模化に不可欠な要素技術が、先進パッケージング技術だと言えよう。

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

AIサーバの高性能化に不可欠となった先進パッケージング技術

AIサーバの高性能化に不可欠となった先進パッケージング技術

2025年12月の国際学会IEDMで、TSMCが最新のパッケージング技術について講演した。本シリーズは、その内容の一部を紹介する。 メモリとストレージの動向を示す11個のキーワード(前編)

メモリとストレージの動向を示す11個のキーワード(前編)

2025年8月に開催された「FMS」の講演を紹介するシリーズ。今回はメモリとストレージの市場アナリストとして知られるJim Handy氏の講演を前後編でご紹介する。 2026年のHBM市況、カギを握るのは最新世代「HBM4」

2026年のHBM市況、カギを握るのは最新世代「HBM4」

2025年8月に開催された「FMS(the Future of Memory and Storage)」の一般講演を紹介するシリーズ。今回はTrendForceのアナリストであるEllie Wang氏の講演を取り上げる。広帯域メモリ(HBM)の生産能力や容量、価格を予測する。 創刊前の20年間(1985年〜2005年)で最も驚いたこと:1985年の「不可能」二題

創刊前の20年間(1985年〜2005年)で最も驚いたこと:1985年の「不可能」二題

EE Times Japan 創刊20周年に合わせて、半導体業界を長年見てきたジャーナリストの皆さまや、EE Times Japanで記事を執筆していただいている方からの特別寄稿を掲載しています。今回は、40年以上にわたり半導体技術/電子技術を見守り、フリーの技術ジャーナリストとして活躍されている福田昭氏にご寄稿いただきます。EE Times Japan創刊からさらに20年さかのぼり、1985年の話からスタートします。 キオクシアの年度業績、3年ぶりの黒字転換で過去2番目の営業利益を計上

キオクシアの年度業績、3年ぶりの黒字転換で過去2番目の営業利益を計上

キオクシアホールディングスの2024会計年度通期(2024年4月〜2025年3月)の決算概要を説明する。 自動車通信システムの国際標準に合わせた周波数割り当ての再編成

自動車通信システムの国際標準に合わせた周波数割り当ての再編成

今回は、高度道路交通システム(ITS:Intelligent Transport Systems)の無線通信用周波数帯域の再編成について解説する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増