10年で5世代の進化を遂げた高性能パッケージング技術「CoWoS」(前編):福田昭のデバイス通信(334) TSMCが開発してきた最先端パッケージング技術(7)

今回からは、高性能コンピューティング(HPC)向けパッケージング技術「CoWoS(Chip on Wafer on Substrate、コワース)」を解説する。

インターポーザの異なる3種類の「CoWoS」

高性能プロセッサとその関連技術に関する国際学会「Hot Chips」がことし(2021年)8月22日〜24日にオンラインで開催された。「Hot Chips」は高性能プロセッサの最新技術情報を入手できる貴重な機会として知られている。会期は3日間で、初日が「チュートリアル(Tutorials)」と呼ぶ技術講座、2日目と3日目が「カンファレンス(Conference)」と呼ぶ技術講演会となっており、講演会とは別にポスター発表の機会も用意される。オンライン開催となったことしは、あらかじめ録画されたビデオをプログラムに沿って公開する形式となった。参加登録者は開催後も一定の期間は、オンデマンドで講演を聴講できる。

初日の「チュートリアル(Tutorials)」では、13件の講演が実施された。その中で「先進パッケージング技術」に関する講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」が極めて興味深かった。講演者はTSMCで研究開発担当バイスプレジデント(現在はシステム集積化手法開発担当バイスプレジデント)をつとめるDouglas Yu氏である。

そこで本講演の概要を第328回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」のアウトライン[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」のアウトライン[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)第330回から前回まではモバイル向け小型薄型パッケージング技術「InFO(Integrated Fan-Out、インフォ)」の改良版を説明してきた。今回からは、高性能コンピューティング(HPC)向けパッケージング技術「CoWoS(Chip on Wafer on Substrate、コワース)」を解説していこう。

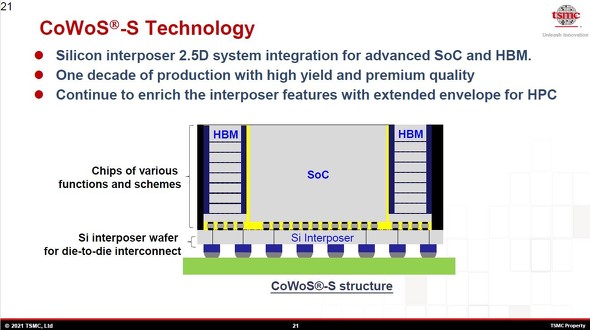

本シリーズの初回(第328回)でも説明したように、TSMCは「CoWoS」を中間基板(インターポーザ)の違いによって3種類に分けている。1つはシリコン(Si)基板をインターポーザとする「CoWoS_S(Silicon Interposer)」である。このタイプは2011年に開発された最初の「CoWoS」技術であり、過去に「CoWoS」とは、シリコン基板をインターポーザとする先進パッケージング技術を意味していた。

もう1つは再配線層(RDL)をインターポーザとする「CoWoS_R(RDL Interposer)」である。3つ目は、シリコンの小さなダイ(チップ)とRDLをインターポーザとする「CoWoS_L(Local Silicon Interconnect and RDL Interposer)」だ。なお「Local Silicon Interconnect」をTSMCは「LSI」と略記することが多いので、留意されたい。

「CoWoS_S」(従来の「CoWoS」)の断面構造例。いわゆる2.5次元(2.5D)パッケージの代表である。中間基板(インターポーザ)であるシリコン基板に高密度な配線とシリコン貫通ビア(TSV)を形成することで、シリコンダイ間の近接配置を可能にするとともに、高速の信号を伝送する[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

「CoWoS_S」(従来の「CoWoS」)の断面構造例。いわゆる2.5次元(2.5D)パッケージの代表である。中間基板(インターポーザ)であるシリコン基板に高密度な配線とシリコン貫通ビア(TSV)を形成することで、シリコンダイ間の近接配置を可能にするとともに、高速の信号を伝送する[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)インターポーザ面積とトランジスタ数、メモリ容量の拡大を継続

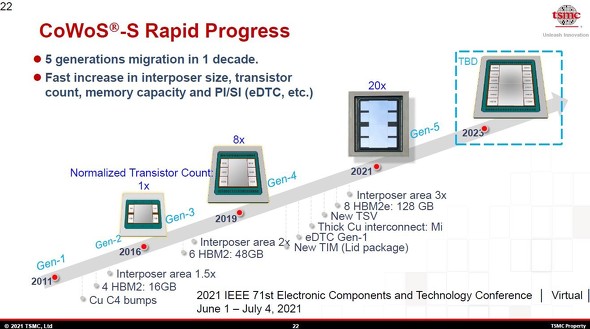

「CoWoS_S」(従来の「CoWoS」)は、2011年に開発された。これを「第1世代(Gen-1)」と呼んでいる。XilinxのハイエンドFPGAなどが採用した(参考記事:「シリコンインターポーザを導入した高性能パッケージの製品例」)。Siインターポーザの大きさは最大で775mm2(25mm×31mm)である。ほぼレチクル1枚の露光寸法(26mm×33mm)に近い(ArF液浸スキャナーの場合)。なおFPGAダイの製造技術は28nmのCMOSプロセスである。この技術を採用したXilinxのハイエンドFPGA「7V2000T」は、4枚のFPGAロジックダイを「CoWoS_S」に搭載した。

2014年に開発された第2世代の「CoWoS_S」では、Siインターポーザを1150mm2に拡大した。レチクル1.5枚の露光面積である1287mm2に近い。2015年にXilinxのハイエンドFPGA「XCVU440」が採用した。3枚のFPGAロジックダイを搭載している。FPGAダイの製造技術は20nmのCMOSプロセスである。

2016年に開発された第3世代の「CoWoS_S」では、Siインターポーザの大きさはあまり変わらないものの、高速DRAMモジュール「HBM」とロジックを初めて混載した。2016年にNVIDIAのハイエンドGPU「GP100」が採用した。GPUダイと「HBM2」を混載する。HBM2はシリコンダイ積層モジュール(4枚のDRAMダイと1枚のベースダイ(最下部)をTSVで接続)で、「GP100」には4個のHBM2モジュールを搭載した。16GB(128Gビット)と大きな容量のDRAMとGPUを高速に接続している。

2019年に開発された第4世代の「CoWoS_S」では、Siインターポーザの寸法をレチクル2枚に相当する露光面積まで拡大した。およそ1700mm2に達する。この巨大なインターポーザに大規模ロジックのダイと6個のHBM2を混載する。1個のHBM2が記憶する容量は8GB(64Gbit)に増加したので、合計では48GB(384Gbit)と第3世代の3倍の容量を収容した。

「CoWoS_S」(従来の「CoWoS」)の進化。2011年の第1世代から、2021年の第5世代まで改良を重ねた[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

「CoWoS_S」(従来の「CoWoS」)の進化。2011年の第1世代から、2021年の第5世代まで改良を重ねた[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)(後編に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

「システム・製造協調最適化(STCO)」の実現技術(前編)

「システム・製造協調最適化(STCO)」の実現技術(前編)

7nm以降の技術ノードでは、「設計・製造協調最適化(DTCO)」だけでなく、「システム・製造協調最適化(STCO:System Technology Co-Optimization)」も利用することでPPAあるいはPPACのバランスを調整することが求められるようになってきた。 「システム・製造協調最適化(STCO)」の実現技術(後編)

「システム・製造協調最適化(STCO)」の実現技術(後編)

本シリーズの最終回となる今回は、前回に続き「システム・製造協調最適化(STCO)」を解説する。 欧州が欧州半導体法「European Chips Act」の策定へ

欧州が欧州半導体法「European Chips Act」の策定へ

欧州委員会委員長であるUrsula von der Leyen氏が2021年9月15日(現地時間)、一般教書演説の中で、「European Chips Act(欧州半導体法)」の策定に関する発表を行った。中国政府が半導体イノベーションに数十億米ドル規模の資金を投じていることや、米国議会が半導体の戦略的価値について合意に達したことなどを受け、EUは、主体的な最先端技術の実現を目指す法案を策定し、競争に参入していく考えを表明した。 第4世代R-Car SoCも発表、ルネサスが語る車載戦略

第4世代R-Car SoCも発表、ルネサスが語る車載戦略

ルネサス エレクトロニクスは2021年10月6日、オンラインで記者説明会を実施。同社オートモーティブソリューション事業本部の事業本部長、片岡健氏が車載事業戦略について語った。 埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説する。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(前編)

- EVに吹く逆風 デンソーの焦りとロームが求める勝機とは

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(後編)

- 石炭灰から「レアアース元素」を回収、新日本繊維【訂正あり】

- 半導体産業を下支え 台湾スタートアップの「3つの特徴」とは

- 「27年度後半の2nm量産誓う」 Rapidus、解析センター開設

- AIと地政学リスクが招く深刻なメモリ危機

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 経産省、Rapidusに6315億円追加支援 「国益のため必ず成功」

- 26年の半導体市場は64%成長で1.3兆ドルに NAND価格は234%上昇