EE Times Japan >

連載記事 >

第15回 差動対の利得を理解する:Analog ABC(アナログ技術基礎講座)(2/3 ページ)

» 2010年07月06日 00時00分 公開

[美齊津摂夫,ディー・クルー・テクノロジーズ]

バランスで利得が変わる

(5)式の「I1/Vt」は本連載の第5回にも登場した通り、エミッタ接地増幅回路の利得を決める計算式です。

差動対は、2つのトランジスタの半分だけを見ると、エミッタ接地回路と同じように考えることができます。(5)式に1/2が付いているのは、反対側(負荷抵抗Rc2の側)のトランジスタに流れるI2の効果「I2/Vt」が影響しているためです。

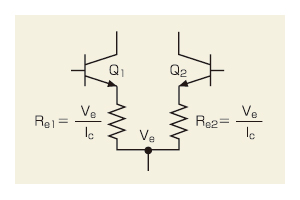

片側のトランジスタのみに信号を入れたとき、信号と入れたのと逆のトランジスタの電流も、入力信号に応じて変化します。I1 とI2の総和は一定ですので、I1が変わると、当然I2も変化します。このため、(5)式の利得の計算式に「1/2」が付くことになります。図3のように、Q1とQ2のエミッタにそれぞれ等価的に抵抗が入っていると考えると分かりやすいと思います。

図3 エミッタの等価抵抗の影響 トランジスタの熱電圧によるエミッタの等価抵抗の効果で、片側のトランジスタのみに信号を入力したときの差動対の利得には、「1/2」の項が付きます。熱電圧とは、温度とボルツマン定数、素電荷で決まるトランジスタのパラメータです(本連載の第6回を参照して下さい)。

図3 エミッタの等価抵抗の影響 トランジスタの熱電圧によるエミッタの等価抵抗の効果で、片側のトランジスタのみに信号を入力したときの差動対の利得には、「1/2」の項が付きます。熱電圧とは、温度とボルツマン定数、素電荷で決まるトランジスタのパラメータです(本連載の第6回を参照して下さい)。また、ΔVin=0とは、差動対がバランスしていることを意味します。2つのトランジスタがバランスすれば、コレクタ電流が同じだけ、双方のトランジスタに流れ、このときに利得は最大になります。

もしバランスが崩れてしまうと、どちらかのコレクタ電流が増え、もう片側は減ります。コレクタ電流が減る側のトランジスタは、利得が減少するのは当たり前なのですが、実はコレクタ電流が増えた側のトランジスタも利得が減ってしまいます。なぜなら、反対のトランジスタの電流が減るので、等価的なエミッタ抵抗(図3のRe1またはRe2)が増えてしまうからです。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR