静電気放電(ESD)対策の新動向、耐圧規格値引き下げの取り組み進む(後編):実装技術

静電気放電(ESD:ElectroStatic Discharge)への対策は、半導体チップの保護に無くてはならないものだ。ESDに伴って発生したパルス状の高電圧は、半導体チップの内部回路を破壊してしまう。

→「The Industry Council on ESD Target Levels」の活動を紹介した「前編」

現状のESD対策は過剰

静電気放電(ESD:ElectroStatic Discharge)への対策は、半導体チップの保護に無くてはならないものだ。ESDに伴って発生したパルス状の高電圧は、半導体チップの内部回路を破壊してしまう。そこで半導体チップには、内部回路を保護するためのESD対策回路を入出力部や電源端子部に実装する。高電圧が印加されたことで発生する電流をグラウンドに逃すことで電圧クランプを施し、内部回路を保護する。

ESDに対する半導体チップの耐圧レベルが高ければ高いほど、半導体チップの信頼性も高まるように思えてしまうが、それは誤解だという。The Industry Council on ESD Target Levelsが、ESD対策回路の耐圧を下げようと提案しているのには、理由と根拠がある。重要なことは、以下の3点である。

1つ目は、半導体チップが微細化するにつれて、これまでと同等のESD耐性を維持するのが極端に難しくなってきたことである。半導体チップの微細化に伴ってトランジスタのゲート膜圧は薄くなり、この結果、絶縁耐性も下がる。このような状況で、従来と同等性能のESD対策回路を維持するのは、技術的難易度が高い。また、ESD対策回路は、動作速度を高めるのを阻害する要因にもなってしまう。「かつては、要求レベルにESD耐圧を合わせることは、それほど困難ではなかった。ところが、製造技術が100nm世代を切るようになってから、技術的な難しさが顕在化してきた」(The Industry Council on ESD Target Levelsのメンバーである磯福佐東至氏*1)という。

2つ目は、半導体チップのESD耐圧を引き下げても、高い信頼性を保ったまま半導体チップを製造・実装できることである。静電気放電を抑えるコントロール技術の進歩が背景にある。

3つ目は、半導体チップのESD耐性と最終機器の段階で要求されるシステム・レベルのESD耐性には因果関係がないという点である。同団体が蓄積したデータなどから因果関係は無いと主張している。「半導体チップの製造時およびプリント基板への実装時のESD対策と、実際の最終機器に組み込んだ後のESD対策は、はっきり分けて考える必要がある。最終機器のESD耐性は、半導体チップのESD耐性の差というよりも、筐体やプリント基板の設計に依存する部分が大きい」(磯福氏)。

以上の3点から導き出される答えが、「ESD保護エリア内で安全な取り扱いと実装の双方の観点から受け入れられる、現実的なESDレベルの提案」(1つ目のホワイト・ペーパーの日本語版)なのである。すなわち、現状で半導体製造/実装工場の静電気コントロールはうまくできるので、半導体チップのESD耐圧を下げても、信頼性はこれまでと何ら変わらないというのが同団体の基本的な考えだ。同団体が過剰品質だと説明するこれまでのESD耐圧を実現するのは、半導体ベンダーや機器メーカーにとって、何のメリットもないとする。

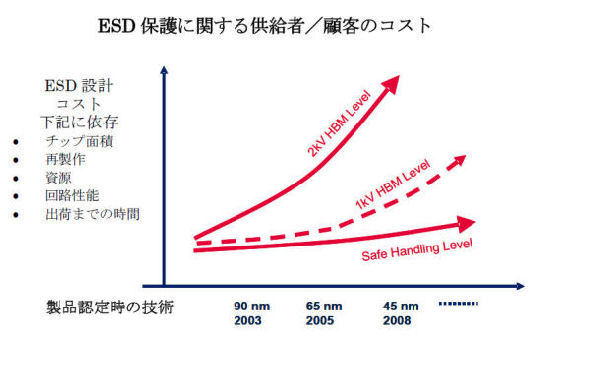

図1 半導体製造技術の進展に対するESD対策回路の設計コスト 半導体製造技術が進展するにつれ、ESD対策回路の設計コストは大きく増える。これまで、人体帯電モデル(HBM)のESD耐圧の規格値は2kVだったが、The Industry Council on ESD Target Levelsではこれを1kVに下げることを、2008年5月に提案した。出典:The Industry Council on ESD Target Levelsが公開したホワイト・ペーパー「A Case for Lowering Component Level HBM/MM ESD Specification and Requirements」

図1 半導体製造技術の進展に対するESD対策回路の設計コスト 半導体製造技術が進展するにつれ、ESD対策回路の設計コストは大きく増える。これまで、人体帯電モデル(HBM)のESD耐圧の規格値は2kVだったが、The Industry Council on ESD Target Levelsではこれを1kVに下げることを、2008年5月に提案した。出典:The Industry Council on ESD Target Levelsが公開したホワイト・ペーパー「A Case for Lowering Component Level HBM/MM ESD Specification and Requirements」これまで半導体ベンダーは、ESD耐圧の要求を満たすために試験やデバッグ、再設計を繰り返してきた。当然のことながら、これらの作業には、手間や時間がかかる。部品コストを引き上げる要因にもなる(図1)。CDMに焦点を当てたホワイト・ペーパーでは、「もはや、最先端の製造プロセスを採用しながら、500VのCDMレベルに対応するのは、設計自体が困難になりつつある」とも指摘している。ESD耐圧規格値の引き下げは、必要かつ待ったなしの取り組みなのである。

CDMでは耐圧250Vを提案

HBMに焦点を当てたホワイト・ペーパーでは、基本的な静電気コントロールがされていれば、HBMのESD耐圧が500Vの半導体チップを安全に取り扱えると説明している。まず、チップ・レベルの規格値として、1kVを推奨した。この目標規格値は、安全に取り扱える500VのESD耐圧に対して余裕を持たせた値である。HBMに焦点を当てたホワイト・ペーパーでは、「HBMのESD耐圧を2kVに設定したチップと、2kV以下に設定したチップの出荷後の信頼性を検証したところ、差はなかった」と報告している。

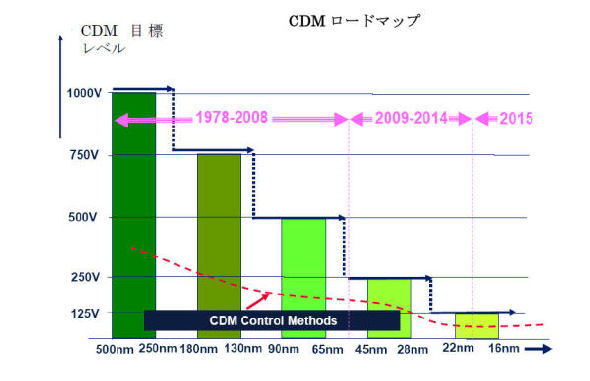

図2 半導体製造技術の進展に対するデバイス帯電モデル(CDM)のESD耐圧の目標レベル 半導体製造技術の進展に伴って、CDMのESD耐圧の目標レベルを段階的に下げることを提案している。すでに公開済みのホワイト・ペーパーでは、これまでの500Vから250Vに下げることを提案している。出典:The Industry Council on ESD Target Levelsが公開したホワイト・ペーパー「A Case for Lowering Component Level CDM ESD Specifications and Requirements」

図2 半導体製造技術の進展に対するデバイス帯電モデル(CDM)のESD耐圧の目標レベル 半導体製造技術の進展に伴って、CDMのESD耐圧の目標レベルを段階的に下げることを提案している。すでに公開済みのホワイト・ペーパーでは、これまでの500Vから250Vに下げることを提案している。出典:The Industry Council on ESD Target Levelsが公開したホワイト・ペーパー「A Case for Lowering Component Level CDM ESD Specifications and Requirements」CDMに焦点を当てたホワイト・ペーパーでは、CDMのESD耐圧の規格値として、250Vを推奨している(図2)。CDMのESD耐圧が250V未満の製品に対しては、静電気コントロールのための工程独自の手段を追加する必要があると説明している。「微細化は継続しており、22nm世代から16nm世代の製造技術では、125Vが新たな目標値となる」(CDMに焦点を当てたホワイト・ペーパー)。

ESD対策技術の教育も必要

磯福氏は、半導体業界のESD対策の参考になる事例として、ハードディスク業界の事例を挙げた。HDDでは、記録密度を高めるために新しい磁気ヘッド構造を採用したのに伴って、ESD耐圧は大幅に下がった。しかし、製造工程での静電気コントロールをきちんと施すことで十分な信頼性を確保している。一般消費者がHDDを使用する際に、ESDの発生を気にすることはない。「この成功例は、半導体業界も参考にできること」(同氏)。

また同氏は、「ESD対策は縁の下の力持ちかもしれないが、ESD対策回路が無ければチップは売れない。日本は、ESD対策の観点から、半導体技術が立ちゆかなくなる可能性があると危惧(きぐ)している」と語った。中国や韓国、台湾、シンガポール、欧米の各国には、高等教育機関でESD対策について学ぶ課程が数多くある。これに対して、日本の大学には、ESD対策について学ぶ課程がほとんど無いことを懸念しているという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- 加賀電子が新光商事にTOB、完全子会社化へ

- 地政学が変えるメモリ調達戦略 「安く買う」だけでは危険