第32回 MOSFETのオペアンプを改善〜裏返し回路で入出力特性向上〜:Analog ABC(アナログ技術基礎講座)(1/2 ページ)

第29回以降、バイポーラトランジスタの替わりに、MOSFETを使ってオペアンプを設計してきました。今回は、いよいよMOSFETを使ったオペアンプ設計編の最終回です。電源電圧付近で出力電圧が入力に追従できないという問題は前回解決しました。そこで、残されたGND側の特性の改善に取り組みましょう。

本連載では第29回以降、バイポーラトランジスタの替わりに、MOSFETを使ってオペアンプを設計してきました。設計したオペアンプをボルテージフォロアとして使ったところ、グラウンド(GND)電圧や電源電圧の付近で、出力電圧が入力電圧に追従できないという現象が発生することが分かりました。

この問題の解決に取り組んだのが、本連載の「第30回 MOSFETのオペアンプを改善〜FET寸法の調整で入出力特性を向上〜」と「第31回 MOSFETのオペアンプを改善〜FETを変えず回路の工夫で特性向上〜」です。今回は、いよいよMOSFETを使ったオペアンプ設計編の最終回です。電源電圧付近で出力電圧が入力に追従できないという問題は前回解決しました。そこで、残されたGND側の特性の改善に取り組みましょう。

nチャネル差動対をpチャネルに変更

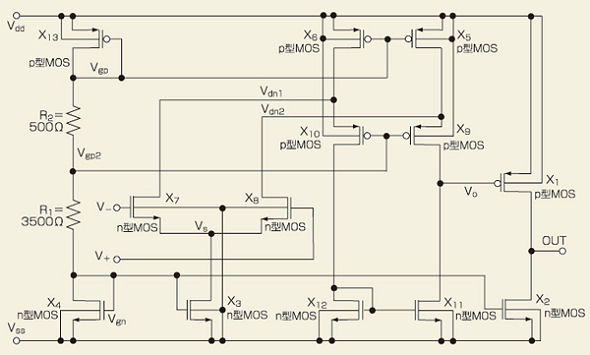

GND側の特性を改善する基本方針は、「裏返し回路」を使うことです。前回(第31回)では、図1に示したように入力段の差動対(X7とX8)にnチャネルのMOSFETを使ったオペアンプを紹介しました。この回路を使って電源側の特性を改善できましたので、nチャネルのMOSFETをpチャネルのMOSFETに置き換えることでGND側の特性改善を進められます。

図1 前回(第31回)までに設計したオペアンプ ボルテージフォロアとして使ったときに、電源電圧付近で出力電圧が入力電圧に追従できないという問題の解決を図った回路です。まだ、GND電圧付近の出力特性を改善できていなかったので、今回挑戦します。

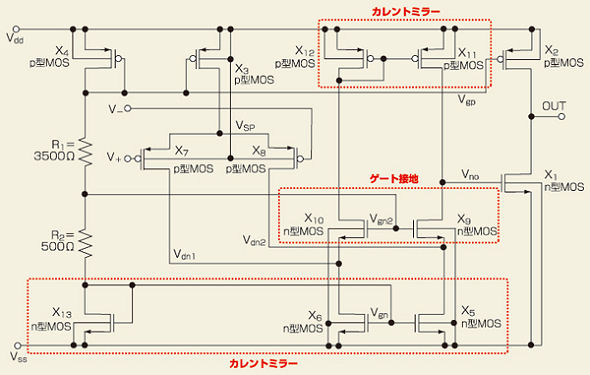

図1 前回(第31回)までに設計したオペアンプ ボルテージフォロアとして使ったときに、電源電圧付近で出力電圧が入力電圧に追従できないという問題の解決を図った回路です。まだ、GND電圧付近の出力特性を改善できていなかったので、今回挑戦します。まずは、入力段の差動対のX7とX8をpチャネルに変更します。この変更に伴って、電流源として動作しているX3とX4もpチャネルのMOSFETに置き換えます。さらに、カスケード(従続)接続されている電流源であるX5とX6、X9、X10をnチャネルに、カレントミラーとして動作するX11とX12をpチャネルにそれぞれ変更します。そして最後に、出力段のX1とX2を入れ替えます。

これらの変更を施した改良後のオペアンプが図2です。図1と図2でMOSFETには同じ番号を振ってありますので、どのように回路が変わっているか確認してみてください。それでは早速、前回と同じようにオペアンプをボルテージフォロアとして使って、直流(DC)特性を確認してみましょう(図3)。

まずGND電圧付近の動作を確認

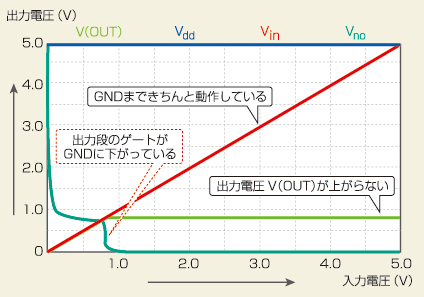

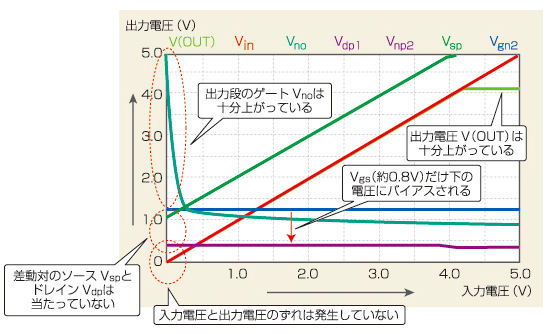

まず見るべきポイントは、GND電圧付近の動作です。十分に動作は改善されていて、入力電圧と出力電圧にずれはありません。第31回の図3または図5を見ると明らかですが、これまでは、出力電圧が入力電圧に追従せず、両者にずれが生まれていました。

グラフ全体を見ると、まだ問題があることに気付きます。出力電圧が0.8Vで止まってしまい、この値以上に上がろうとしません。nチャネルのMOSFETからpチャネルのMOSFETへの変更には問題が無いはずですが、どこが悪いのでしょうか。

設計した回路の動作を一つ一つ追ってみると、出力MOSFETであるX1のゲート電圧VnoがGND電圧まで下がっていることが分かりました。図4の水色のラインを見てください。入力電圧が1Vの付近からVnoは0Vに下がってしまっています。つまり、ゲート電圧が0Vということは、X1は完全にオフ状態になっており、増幅器として動作していないことが分かります。

図4 図3のボルテージフォロアの入出力特性 GND電圧付近でも、出力電圧が入力電圧の変化に追従していることが分かります。ただ、出力電圧の上昇が0.7Vで止まってしまっています。この点を改善する必要があります。

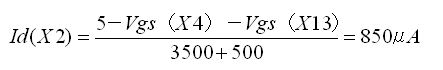

図4 図3のボルテージフォロアの入出力特性 GND電圧付近でも、出力電圧が入力電圧の変化に追従していることが分かります。ただ、出力電圧の上昇が0.7Vで止まってしまっています。この点を改善する必要があります。そうなると、出力電圧を決めているのは、pチャネルのX2だけとなり……X2には一定の電流しか流れない……電源電圧が5Vなので、以下の計算式の電流しか流れないということに気付きます。

ここで、Vgs=0.8Vと設定しました。オペアンプの出力には、負荷抵抗R1の1kΩが出力端子とGND端子間に接続されているので、1kΩ×850μA=0.85Vにしか、出力電圧が上がらないのは、納得するところです。

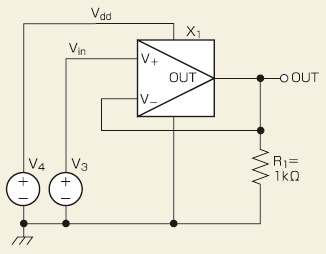

上に説明した問題を解決するために、負荷抵抗R1を挿入する位置を、出力端子とGND端子の間ではなく、出力端子と電源端子の間に変更しました(図5)。

今度はうまくいったようです(図6)。出力電圧V(OUT)は、4Vを超えたところまで上がりました。なぜ、電源電圧の5Vまで上がらずに、4Vで止まってしまうかというと、入力電圧と出力電圧がともに高くなるので、差動対のX7とX8のソース電圧Vspも電源電圧に近づきます。そうなると、電流源X3のソース-ドレイン電圧Vdsが小さくなり、最後には線形領域に入って、電流が減少してしまいます。この結果、オペアンプの利得が保たれなくなり、入力電圧と出力電圧にずれが生じるのです。

この点は、前回の本連載で説明した通り、nチャネルのMOSFETを使ったとき、出力電圧をGND電圧付近まで下げられなかった原因と同じです。解決方法は、前回の「n型とp型のしきい値の差を考慮」の段落にまとめてありますので、参考にしてください。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

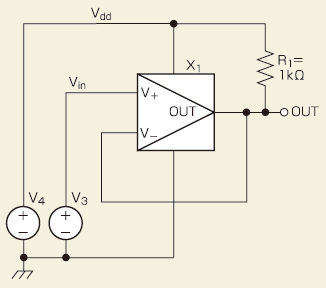

図3 出力端子とGND端子の間に負荷を挿入したボルテージフォロア

図3 出力端子とGND端子の間に負荷を挿入したボルテージフォロア

図5 出力端子と電源端子の間に負荷を挿入したボルテージフォロア

図5 出力端子と電源端子の間に負荷を挿入したボルテージフォロア 図6 図5のボルテージフォロアの入出力特性 出力電圧は0.7Vを超え、4.0V付近まで上昇させることができました。

図6 図5のボルテージフォロアの入出力特性 出力電圧は0.7Vを超え、4.0V付近まで上昇させることができました。